Heraeus Electronic

應用在通訊終端中的功率放大器 (PA,Power Amplifier) 已經成熟批量生產。隨著電子設備朝高性能、小型化和封裝成本的要求發展,高密度封裝成為必然趨勢。在這一背景下,DA295A 無壓燒結銀為高密度、高性能的封裝(LGA/QFN) 提供了理想的 GaAs、GaN 芯片與基板互連解決方案。

高密度封裝指在一條基板上會有 2000 到 3000 顆獨立的芯片。這種封裝在 die bond 過程中通常會面臨點膠/畫膠的穩定性、RBO(樹脂溢出)、open time(點膠到裝芯片的停留時間)以及銀膏覆蓋率的挑戰。賀利氏研發團隊通過修改配方和工藝流程等方案克服了這些挑戰。

- 畫膠圖案:Double Y

- 畫膠速度:70% (ESEC 2100)

- 畫膠壓力:0.85 bar

產品結構:高密度基板,一條基板有3200多顆GaAs芯片需要貼裝。

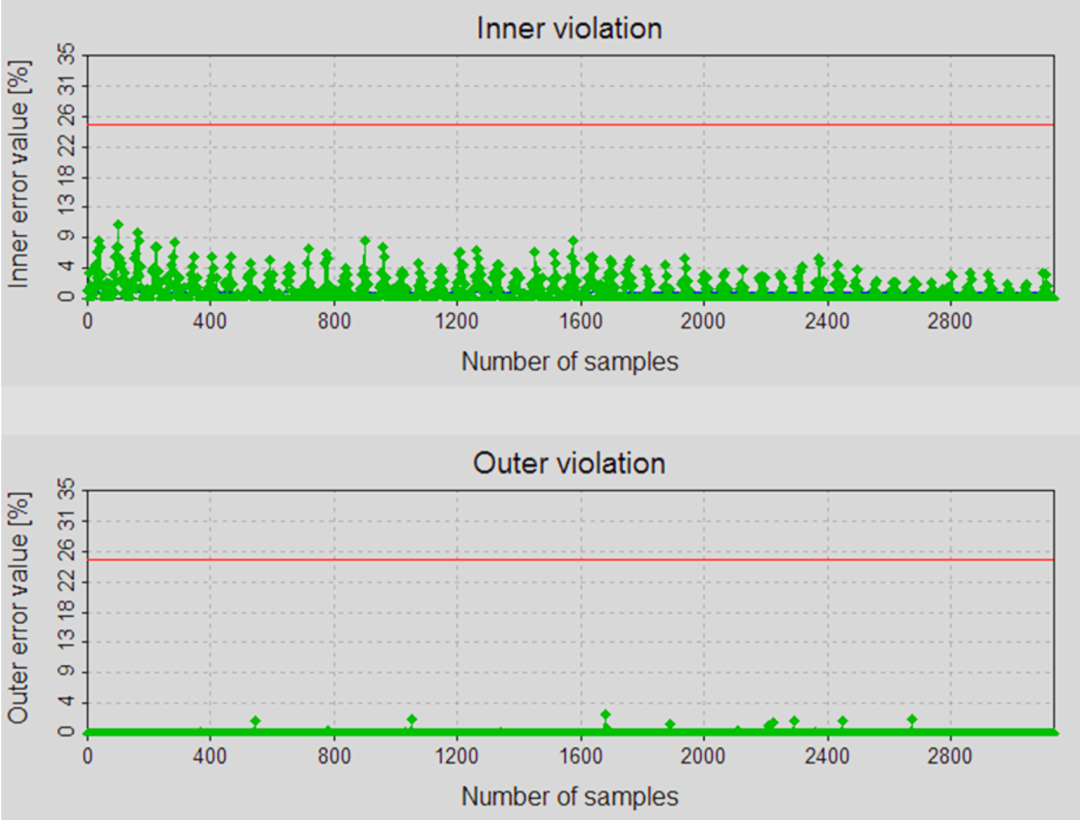

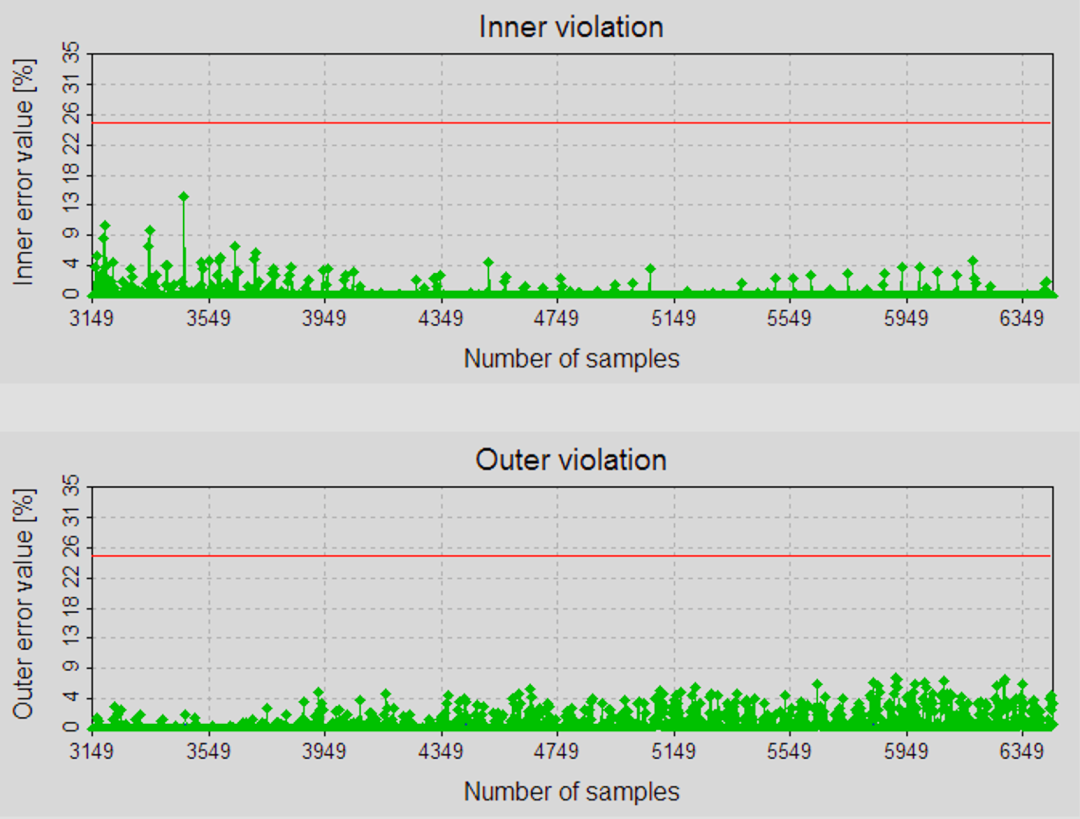

測試方法:使用相同的參數連續畫膠

判斷標準:基于ESEC2100對膠形的檢測,客戶設定的規格膠型變化<25%

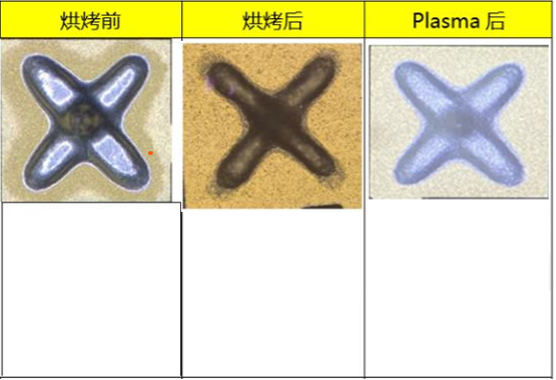

RBO(樹脂溢出,Resin Bleeding Out)在烘烤過程中無法去除,也無法在wire bonding前的等離子清洗中完全清除,因此對打線和封裝會產生一定影響。

賀利氏的ASP/DA295系列產品均采用無樹脂添加的溶劑配方體系,即全燒結配方體系(燒結完成后無殘留樹脂成分)。溶劑配方體系通常使用沸點較低的溶劑,在烘烤過程中達到沸點后溶劑將會揮發掉。

在實際實驗中,不同的基板DPAD表面處理會導致不同程度的溶劑溢出,如下圖所示。圖3-1展示了較少的溶劑溢出,而圖3-2則顯示了接近100%的溶劑溢出。

溶劑溢出(Solvents bleeding out)在烘烤前后和等離子清洗后我們做了對比測試,如表1所示:

*備注:顯微鏡的燈光影響了照片的顏色

選用常見芯片尺寸(mm):0.74*0.70

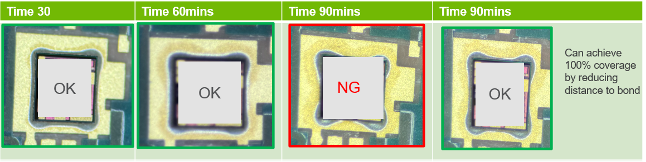

測試條件:使用相同的畫膠參數以獲得一致的膠量,在同一時間畫膠,根據不同的時間間隔使用相同的參數進行貼裝芯片。

判斷標準:在BLT(Bond Line Thickness)在20~30um內,銀膏覆蓋率達到100%。

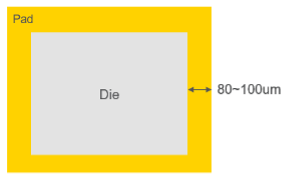

高密度封裝意味著在當前標準的基板尺寸內排列更多的個體單元,即減小焊盤尺寸壓縮芯片的貼裝面積。

在高密度封裝中,芯片邊緣到焊盤的距離變得更小,例如有些產品設計了80~100um的距離,如圖5所示。

測試方法:通過控制畫膠圖案的尺寸和裝片的高度,在裝片時控制銀膏的溢出。

檢測方法:在顯微鏡下檢查芯片底部銀膏覆蓋。

判斷標準:銀膏覆蓋率達到100%,且沒有超出焊盤。

●?改善版的DA295A具有穩定的作業性。

●?溶劑體系的配方在烘烤后溢出的溶劑能夠揮發掉,不會對打線鍵合產生影響。

●?較長的open time能夠滿足高密度封裝的需求,避免分段式作業。

●?能夠解決緊湊型設計的銀膏覆蓋率問題。

原文始發于微信公眾號(賀利氏電子):技術博客|適用于高密度封裝的無壓燒結銀方案