在之前的技術文章中,介紹了驅動芯片的概覽和PN結隔離(JI)技術,本文會繼續介紹英飛凌的絕緣體上硅(SOI)驅動芯片技術。

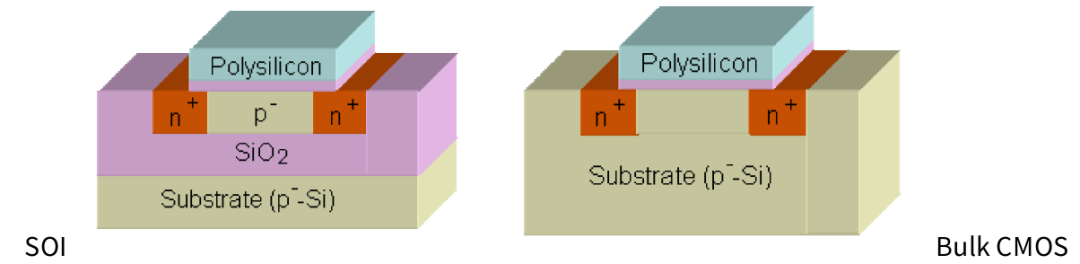

高壓柵極驅動IC的技術經過長期的發展,走向了絕緣體上硅(silicon-on-insulator,簡稱SOI),SOI指在硅的絕緣襯底上再形成一層薄的單晶硅,相對于傳統的導電型的硅襯底,它有三層結構,第一層是厚的硅襯底層,用于提供機械支撐,第二層是薄的二氧化硅層,二氧化硅是一種絕緣體,從而形成一層絕緣結構,第三層是薄的單晶硅頂層,在這一層進行電路的刻蝕,形成驅動IC的工作層。

圖1.絕緣體上硅SOI(左圖)與傳統體硅(Bulk CMOS)(右圖)結構的比較

SOI在1964年由C.W. Miller和P.H. Robinson提出,經過幾十年的發展,逐漸成熟。英飛凌采用了SOI的獨特設計的柵極驅動IC,從設計上帶來了諸多優勢。其中,最大的優勢在于,SOI的二氧化硅的絕緣層,能夠徹底消除體硅(Bulk CMOS)結構中襯底中的寄生PN結,從而消除了閉鎖效應,提高了驅動芯片耐受負壓的能力。

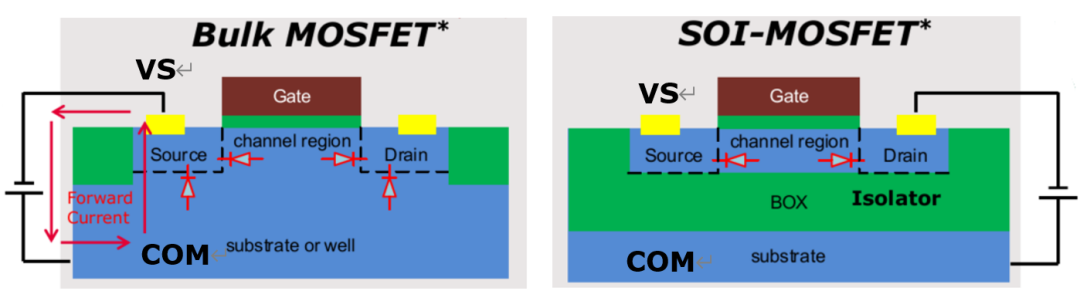

圖2.傳統體硅(Bulk CMOS)(左圖)與絕緣體上硅SOI(右圖)寄生PN結的比較

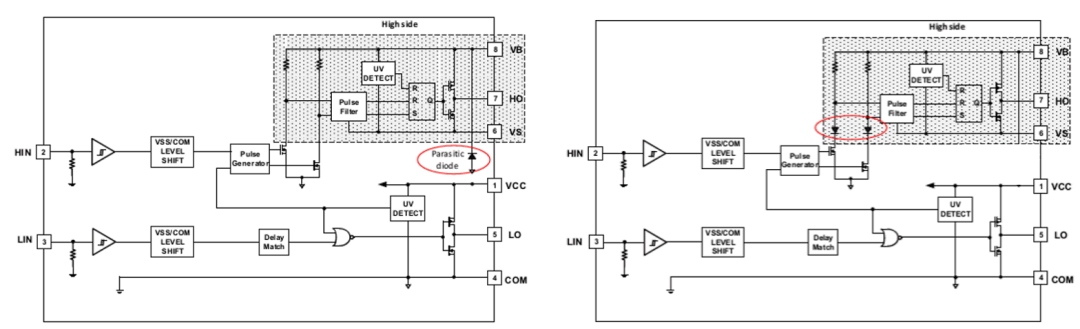

從柵極驅動IC的設計結構上,如圖3所示,可以清楚的看到相關電路的影響,在體硅(Bulk CMOS)的設計中,對于高邊電路,襯底連接COM電位,MOS的源極SOURCE連接VS電位,因為襯底與VS之間存在一個寄生二極管,從而在某些工況下,當COM的電位高于VS的電位時,寄生二極管會導通,產生無法控制的電流,從而對電路的可靠性產生影響。在絕緣體上硅SOI的驅動IC中,因為二氧化硅絕緣層的存在,消除了連接COM和VS的寄生二極管,從而極大提升了驅動IC的可靠性。

圖3.傳統體硅(Bulk CMOS)(左圖)與絕緣體上硅SOI(右圖)寄生PN結對設計的影響

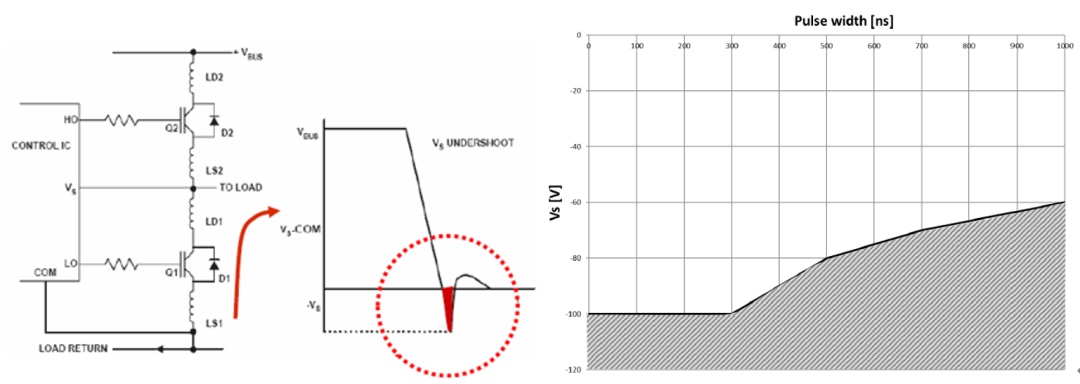

驅動芯片的耐受負壓(VS的電壓低于COM)的能力,對于電機驅動應用,或者橋式電路帶感性負載的應用情況,都非常重要。如圖4所示,當上管Q2關閉的時候,負載電流切換到下管D1,此時電流從負母線流向負載。考慮動態的情況,在D1上的電流逐步建立的過程中,在VS~COM之間,會產生由Ls1和Ld1的感生電壓,以及Q1的二極管的導通電壓,總的電壓等于這三個電壓的疊加,方向上電壓在COM為正,VS為負。因為這類應用中,負壓現象不可避免,所以驅動IC耐受這個負壓的能力越高越好,圖4的右圖可以看出,英飛凌的SOI驅動IC,抗負壓的能力可以達到-100V/300ns或者-60V/1000ns,這種抗負壓的能力遠遠大于JI設計的驅動IC。

圖4.橋式電路中負壓的產生,及英飛凌的SOI驅動的負壓耐受工作區

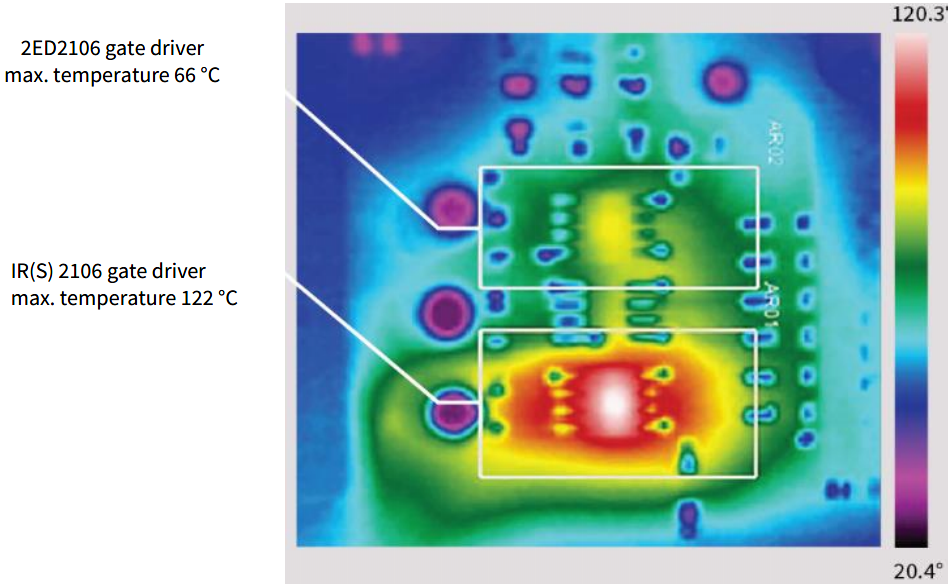

另外,SOI的結構中,因為寄生PN結的消失,器件的寄生效應減小,器件的開關損耗也可極大的降低,并且由于漏電流的減小,靜態功耗也可以得到降低,從而使得采用SOI設計的驅動IC,工作頻率能夠更高,整體損耗更小。圖5對比了300kHz的開關頻率下,2ED2106(SOI設計)與IR2106(Bulk CMOS設計)的溫升對比,可以看到,2ED2106的最高溫度只有66°C,而IR2106的溫度高達122°C。

圖5.絕緣體上硅SOI與傳統體硅(Bulk CMOS)的驅動IC的溫升比較

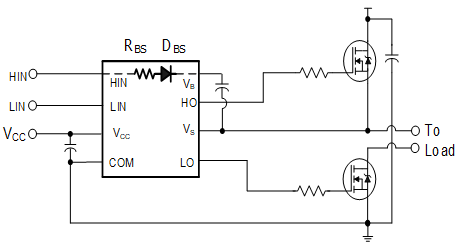

再次,SOI因為存在良好的介質隔離,更方便進行集成。英飛凌的SOI的驅動IC集成了自舉二極管,從而能夠節省掉以前需要外加的高壓自舉二極管,從而節省系統成本。

圖6.絕緣體上硅SOI集成自舉二極管示意圖

綜上所述,絕緣體上硅SOI是柵極驅動器的一次技術飛躍,具有負壓耐受能力強、損耗低、集成自舉二極管等一系列的優異特性。

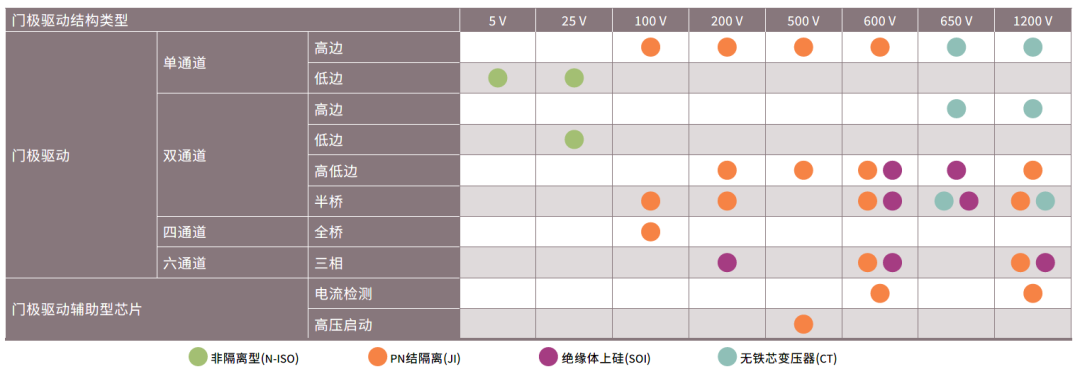

英飛凌已經推出了大量的絕緣體上硅SOI的驅動IC,電壓覆蓋200V至1200V,結構有高低邊驅動、半橋及三相橋。

原文始發于微信公眾號(英飛凌工業半導體):絕緣體上硅(SOI)驅動芯片技術優勢及產品系列

一顆芯片的制造工藝非常復雜,需經過幾千道工序,加工的每個階段都面臨難點。歡迎加入艾邦半導體產業微信群:

長按識別二維碼關注公眾號,點擊下方菜單欄左側“微信群”,申請加入群聊