本文由半導體產業縱橫(ID:ICVIEWS)編譯自tomshardware

英特爾的 IEDM 2022 研究論文講述了有前途的新技術。

英特爾在IEDM 2022上發布了九篇研究論文,為未來的芯片設計奠定了基礎,該公司有望兌現到2030年開發超過萬億晶體管處理器的承諾。

研究包括用于晶體管的新 2D 材料、新的 3D 封裝技術將小芯片和單芯片處理器之間的性能和功率差距縮小到幾乎無法察覺的范圍,斷電時“不會忘記”的晶體管,以及可以直接堆疊在晶體管頂部并存儲多個的嵌入式存儲器每個單元位,以及其他創新。

英特爾的組件研究 (CR) 小組為公司的未來技術奠定了初步基礎,但并非所有這些舉措都會導致產品上市。那些真正上市的產品通常會在五到十年內上市。

該團隊在已經上市的創新方面有著令人難以置信的記錄,例如徹底改變整個行業晶體管設計的 FinFET、應變硅、Hi-K 金屬柵極等。英特爾的路線圖上已經有其他幾項技術,包括RibbonFET Gate All Around (GAA) 晶體管、PowerVia 背面供電、EMIB 和 Foveros Direct,它們都來自該研究小組。

該小組在今年的第 68 屆年度 IEEE 國際電子設備會議上提交了九篇研究論文,下面我們將稍微詳細地介紹其中的幾篇。

來源:英特爾

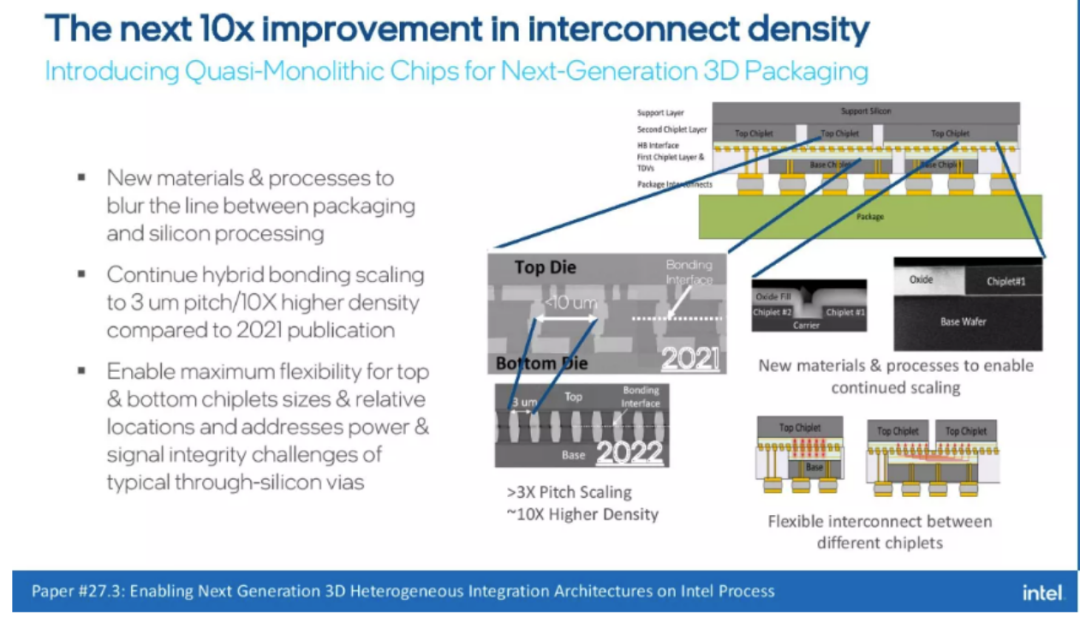

晶體管密度的增長速度大致符合摩爾定律,但當今芯片的經濟性并沒有以同樣的速度提高——隨著我們轉向更密集的節點,每個晶體管的價格正在上漲。此外,一些芯片元件(如模擬和緩存)的擴展性差,使事情進一步復雜化。因此,該行業正在集體轉向基于小芯片的高性能芯片設計。

任何基于 chiplet 設計的首要目標是在利用基于 chiplet 的方法的經濟效益的同時,保留單芯片單片處理器內部數據路徑的功耗和性能(延遲、帶寬)的最佳屬性,例如采用前沿工藝制造的較小芯片提高產量,以及使用較成熟、較便宜的節點來實現密度改進較小的其他一些功能的能力。

因此,半導體霸權的戰場正在從晶體管的速度轉移到互連的性能,硅中介層 (EMIB) 和混合鍵合技術等新技術成為提高經濟性的前沿。

這些方法仍然會導致不可避免的性能、功耗和成本權衡,英特爾新的“準單片芯片”(QMC) 3D 封裝技術希望解決這個問題。顧名思義,英特爾的 QMC 旨在提供與內置在單個芯片中的互連幾乎相同的特性。

QMC 是一種新的混合鍵合技術,其間距小于 3 微米,與英特爾在去年 IEDM 上提交的研究相比,能效和性能密度提高了 10 倍。之前的論文涵蓋了一種 10 微米間距的方法,這已經是 10 倍的改進。因此,英特爾在短短幾年內找到了實現 100 倍改進的途徑,表明該公司在混合鍵合方面的工作正在迅速加速。QMC 還可以讓多個小芯片相互垂直堆疊,如上圖所示。

文章概述了令人難以置信的每平方毫米數十萬個連接的互連密度和可與我們在單片處理器中看到的相媲美的功耗(以每比特皮焦耳 - Pj/b 為單位)。此外,新論文概述了幾種可用于制造此類設備的新材料和工藝,為現實世界的設備鋪平了道路。

英特爾的工藝路線圖已經下降到納米級以下到埃級,盡管節點命名慣例早就與晶體管的實際物理測量失去了聯系,但很明顯,需要一種全新的方法來繼續擴展。大多數行業都押注未來會轉向 2D 原子通道,但與所有新技術一樣,要實現這種根本性的改變需要很多步驟。

今天的芯片材料,如硅,由三維晶體組成,這意味著原子在所有三個維度上都結合在一起,從而對收縮提出了基本限制。相比之下,二維材料很有吸引力,因為所有的原子都鍵合在一個平面上,因此可以用小至三個原子的厚度來構建特征。

英特爾對2D材料的研究,也可以用于3D GAA晶體管。當前的 GAA 設計由堆疊的水平硅納米片組成,每個納米片都被一個門完全包圍。這種“環柵”(GAA) 技術可減少防止晶體管關斷的電壓泄漏。隨著晶體管的縮小,這變得越來越成為一個問題——即使當柵極在三邊圍繞溝道時,正如我們在 FinFET 晶體管中看到的那樣。

英特爾將其 GAA 設計命名為 RibbonFET,目前計劃于 2024 年上半年推出。然而,超越 RibbonFET 將需要進一步的創新,而這項 2D 研究符合潛在途徑的要求。

英特爾的論文描述了一種全環繞柵 (GAA) 堆疊納米片結構,其通道材料(納米片/納米帶)厚度僅為三個原子,可以在室溫下以低漏電流運行。

二維通道材料的厚度使得建立與納米帶的電連接成為一項艱巨的任務,因此英特爾還為二維材料建立了電接觸拓撲模型。這是了解二維材料的特性及其功能的關鍵一步,從而使公司能夠準確地模擬進一步的進步。

各種形式的內存都是計算不可或缺的一部分,但它也在芯片和系統級別消耗大量功率預算,同時也是性能的限制因素。

英特爾還進行了世界上第一個 3D 堆疊鐵電存儲器的功能演示。這項技術最令人印象深刻的方面是鐵電溝槽電容器可以垂直堆疊在晶體管頂部的邏輯芯片上。這使得能夠將存儲器分層在邏輯元素之上,而不是像我們在其他類型的嵌入式存儲器中看到的那樣,將其置于其自己的不同區域中,例如用于 L1 和 L2 緩存的 SRAM。

鐵電存儲器還具有與我們在 NAND 閃存中看到的類似的功能——能夠在通常只存儲一位的結構中存儲多位數據。在這種情況下,英特爾展示了每個溝槽存儲四位的能力。

自然地,這種方法會增加帶寬和內存密度,同時減少延遲,從而產生更大更快的片上緩存。

與二維結構的電接觸建模一樣,英特爾還分享了其對鐵電氧化鉿器件的混合相和缺陷的建模工作,這反過來將進一步推動公司自身的研發過程。

英特爾還在研究“不會忘記”的晶體管,這意味著它們在斷電時不會丟失數據(開/關狀態)。這類似于任何非易失性存儲器,如 NAND,它可以在斷電時保持其狀態,但它以邏輯晶體管的形式出現。英特爾表示,它已經克服了在室溫下使用該技術的三個障礙中的兩個。我們特別期待這次演講。

英特爾在此次活動中的其他論文概述了其他研究領域,如硅片上的氮化鎵(GaN),可以實現5G以外的未來技術,以及存儲量子信息的更好方法,為量子計算創造更好的量子比特。

原文始發于微信公眾號(半導體產業縱橫):英特爾:2D 晶體管材料,3D 封裝研究

成員: 5306人, 熱度: 153517

ceramics?天線?通訊?終端?汽車配件?濾波器?電子陶瓷?LTCC?MLCC?HTCC?DBC?AMB?DPC?厚膜基板?氧化鋁粉體?氮化鋁粉體?氮化硅粉體?碳化硅粉體?氧化鈹粉體?粉體?生瓷帶?Ceramic substrate?氧化鋁基板?切割機?線路板?銅材?氮化鋁基板?氧化鈹基板?碳化硅基板?氮化硅基板?玻璃粉?集成電路?鍍膜設備?靶材?電子元件?封裝?傳感器?導電材料?電子漿料?劃片機?稀土氧化物?耐火材料?電感?電容?電鍍?電鍍設備?電鍍加工?代工?等離子設備?貼片?耗材?網版?自動化?燒結爐?流延機?磨拋設備?曝光顯影?砂磨機?打孔機?激光設備?印刷機?包裝機?疊層機?檢測設備?設備配件?添加劑?薄膜?material?粘合劑?高校研究所?清洗?二氧化鈦?貿易?equipment?代理?其他?LED