在功率轉換中,效率和功率密度至關重要。每一個造成能量損失的因素都會產生熱量,并需要通過昂貴且耗能的冷卻系統來去除。軟開關技術與碳化硅(SiC)技術的結合為提升開關頻率提供了可能;從而能夠縮減暫存能量和用于平滑開關模式轉換器輸出無源元件的尺寸及數量,還為轉換器構建了減少發熱量并由此使用更小散熱片的基礎。

對于傳統的硅基功率晶體管而言,一些效率和頻率上的改進得益于功率轉換器設計中從簡單硬開關向軟開關架構的轉變。這種工藝技術的變革之所以重要,是由于盡管硅技術在提高開關頻率和改善效率方面取得了長足進步,但SiC使得軟開關技術得以更為有效地應用。

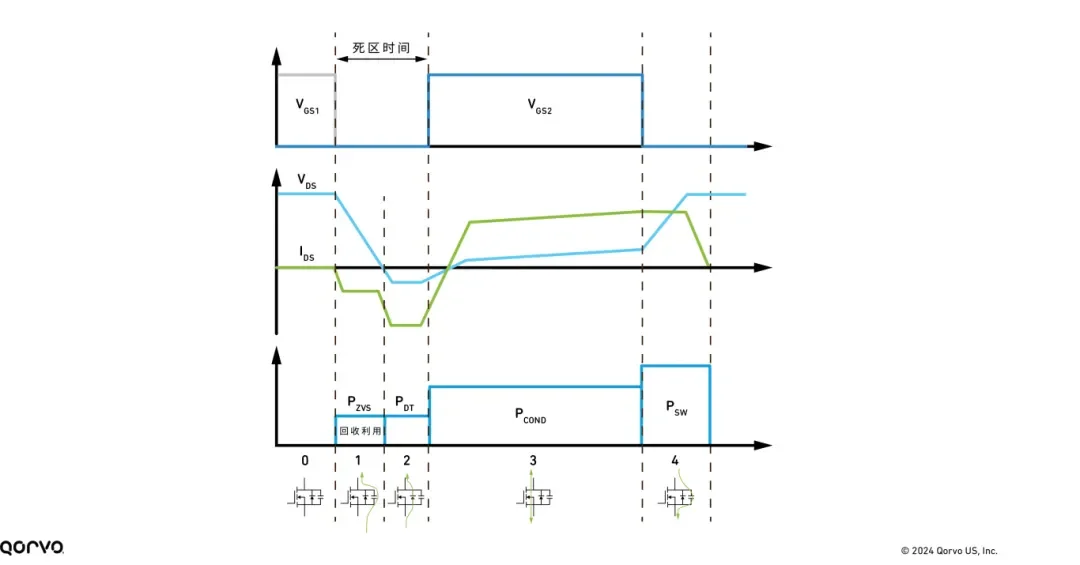

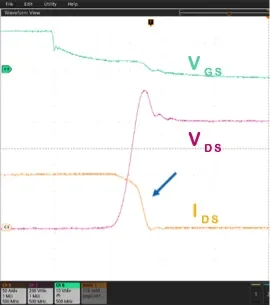

硬開關和軟開關之間的主要區別在于,軟開關減少或消除了功率晶體管在開通和關斷階段默認電壓及電流條件下的損耗。圖1展示了一個零電壓開通(ZVS)技術的典型示例;其用于消除開通時的開關損耗。在電源開關中,其余的主要損耗包括傳導損耗和關斷時的開關損耗。隨著開關頻率的增加,電壓和電流的同步擺動會導致顯著的損耗。從概念上講,軟開關通過調整電壓和電流擺動的時序來減少或消除損耗;但“軟開關”這一術語實際涵蓋了設計師用來限制損耗的多種技術。

圖1,ZVS軟開關波形及不同開關階段半橋電路的主要能量損耗來源

零電壓開通(ZVS)是開通階段最廣泛使用的軟開關形式;它遵循一個簡單的核心原理:在電流能自由通過晶體管溝道之前,減少漏極和源極間的電壓。在開通之前,輸出電容也被充電到與漏-源電壓相同的水平;輸出電容是漏-源電容和柵-漏電容之和。為利用ZVS帶來的優勢,需要將這些存儲的電荷清除至負載中,以避免在開通時漏-源電壓下降和漏-源電流上升同時發生而導致的損耗。理想情況下,當晶體管溝道兩端的電壓較低(已接近零)時,電流開始上升。

盡管ZVS的廣泛應用解決了開關轉換器中最重要的損耗源頭問題,但如果設計師要充分利用更高頻率的工作優勢,還需要密切關注其它損耗源。一些應用正暴露出傳統設計中一些效率低下的問題。諸如大型語言模型等領先AI應用對加速器的要求越來越高,導致這些加速器的工作溫度接近IC封裝的承熱極限;PCB上的每個器件都要消耗數百瓦的功率。其結果是,向承載多核微處理器、圖形處理單元和專用AI加速器的高密度機架所提供的電量急劇增加。

功率需求已達到一個臨界點;其中功率轉換器需要為機架式系統提供高達8kW的電力。在此過程中,它們將從數百伏的交流或直流饋電中取電,并以高電流水平將其轉換為48V電壓,以便分配給各個處理器群。這要求功率轉換器兼具高效率和高密度,并需要承受600V或更高電壓浪涌的故障。由于ZVS軟開關將開通開關損耗降至接近0,因此在ZVS軟開關應用中,功率半導體的主要損耗變為傳導損耗。這使得導致下一個關鍵效率損失的原因成為關注點:即電流通過時晶體管溝道中電阻所引起的傳導損耗。

理想情況下,功率轉換器中的導通電阻應盡可能低。工藝上的改進已幫助硅超結器件滿足了這些需求;但設計師如今可以利用碳化硅(SiC)等寬帶隙技術,在400V至800V母線電壓的應用中充分利用更低電阻所帶來的優勢。

碳化硅(SiC)在高密度功率轉換器中的一個首要優勢在于,它能夠以極低的RdsA(單位面積導通電阻)支持高擊穿電壓;這對于數據中心的部署十分關鍵,因為數據中心的配電電壓需要足夠高,以防止在電源電纜上產生過大的電阻損耗。

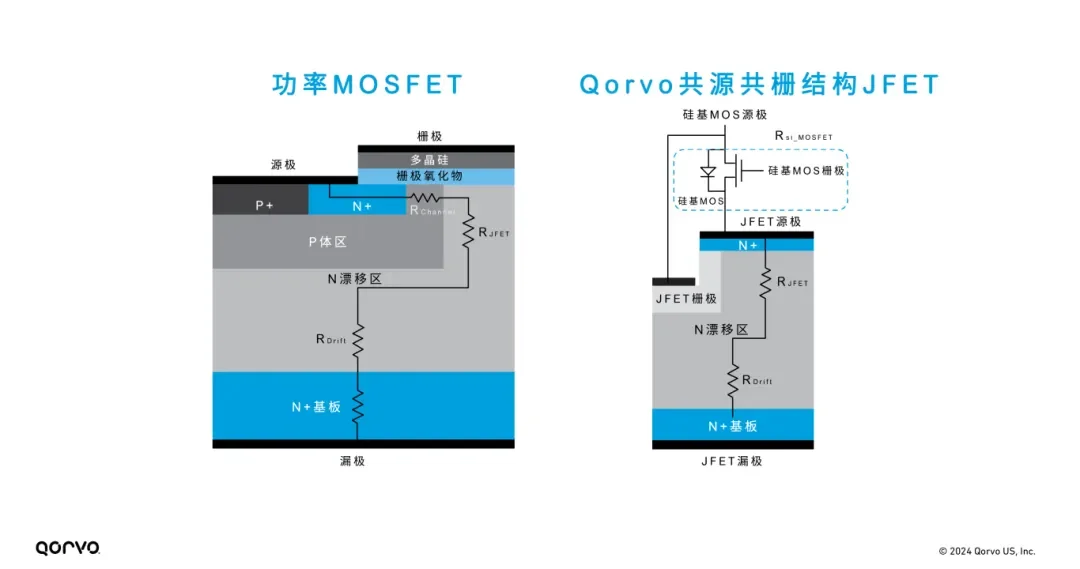

然而,并非所有的SiC器件都完全相同。用SiC的等效器件替換硅超結MOSFET以充分利用效率和功率密度方面的改進,似乎是一個誘人的選擇。基于SiC的設計還帶來了其它機會,使得將MOSFET結構替換為能夠大幅降低導通電阻的結構變得更具價值。對此,結型場效應晶體管(JFET)結構提供了關鍵優勢。它具有概念上更簡單的結構(如圖2中右下部分所示);此外,得益于載流子無需先通過類似MOSFET的溝道再進入連接至漏極的n型漂移區,因而能夠實現更低的整體電阻。這讓導通電阻更接近由擊穿電壓所決定的理論極限值;使得JFET與MOSFET相比,在擊穿電壓方面能提供更高的安全裕量,同時每單位面積的導通電阻更低。

圖2,SiC MOSFET與用于共源共柵電路SiC JFET的截面比較

JFET在功率電路中應用較少使用的一個原因是它作為一種常開型器件,需要負電壓才能完全關斷。通過使用共源共柵結構,可以實現更類似于MOSFET(常關)的控制。這種結構將SiC JFET與低壓硅基MOSFET串聯。在共源共柵結構中采用低電壓硅基器件,如圖2右上部分所示,可最大限度地減小整體運行電阻;均衡的設計使得MOSFET對總導通電阻的貢獻小于10%。因此,可以將MOSFET和JFET融合在單一封裝中,以便于集成和設計——Qorvo將這種設備類型稱為SiC FET;它與SiC MOSFET有著明顯的區別。

通過使用低電壓硅基MOSFET將控制柵極與JFET分離,可以避免通常會降低基于MOSFET設計性能的其它折衷。柵極控制的解耦使得可以在不犧牲SiC性能的前提下優化柵極電壓及其相關電荷。標準的SiC MOSFET通常需要較高的柵極電壓,往往接近20V,以確保在整個工作溫度范圍內的正確運行。與JFET結合的共源共柵架構使得使用較低的柵極電壓(0V至12V)成為可能,這有助于減少柵極電荷,而柵極電荷正是在開關過程中產生損耗的另一個潛在來源,尤其是在輕負載時對于具有高開關頻率的軟開關應用。

在共源共柵配置中結合使用JFET和硅基MOSFET,進一步帶來了通過降低米勒電容(即柵極到漏極電容,Cgd)來提高效率的機會。高電容會對MOSFET的開關速率產生不利影響。共源共柵結構所實現的改進同樣提升了密度,因為它們使得開關頻率可以高于傳統硅基器件的實用水平。

盡管ZVS避免了開通損耗,但仍然存在死區時間;在此期間沒有功率輸出。這種死區時間在硅基設計中可長達300ns;它減少了每個周期內可用于導通狀態的時長比例,從而限制了最大可用開關頻率。在500kHz的開關頻率(周期為2μs)下,開通和關斷邊緣的死區時間各為300ns,占整個開通周期的30%。相比硅超結MOSFET,SiC JFET的輸出電容降低了10倍,從而顯著縮短了所需的死區時間并提高了頻率。

十分重要的一點是,不應忽視在關斷階段降低損耗的機會,因為這在轉向SiC技術后可能更具優勢。如果不使用額外的電路,當晶體管關斷時,電流和漏-源電壓將同時變化,會導致類似于硬開關在開通階段的損耗。然而,快速關斷除了減少關斷開關損耗,也會在設備漏-源端引入高關斷電壓尖峰和振鈴。

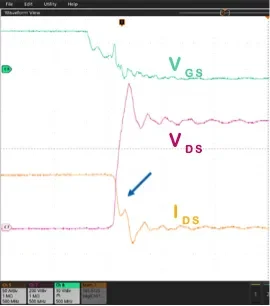

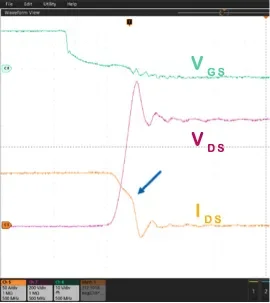

控制關斷漏-源電壓尖峰和振鈴有兩種常見方法。一種是使用高柵極電阻(Rg)來降低器件開關速度;另一種方法是利用低柵極電阻和漏-源RC緩沖器電路來抑制VDS尖峰及振鈴。一個常見的誤解是認為使用緩沖器的效率很低;然而,對于如LLC諧振或相移全橋等經常使用ZVS開關技術的拓撲結構來說,采用緩沖器比高柵極電阻更為高效。在ZVS軟開關應用中,添加的漏-源緩沖電容不會產生任何開通損耗。漏極與源極間額外的緩沖電容與低柵極電阻相結合,在互補續流器件關斷時的dv/dt轉換中提供了更高的位移電流。這進一步減少了關斷電流和電壓之間的重疊;相較于僅使用高柵極電阻,可更大幅度降低關斷開關損耗。通過這種方法,我們能夠在不犧牲器件開關速度的情況下抑制VDS振鈴;而如果采納高柵極電阻的設計策略,則需要犧牲器件開關速度。

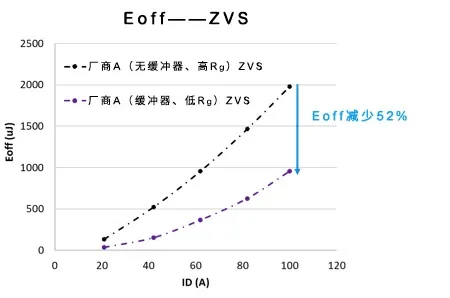

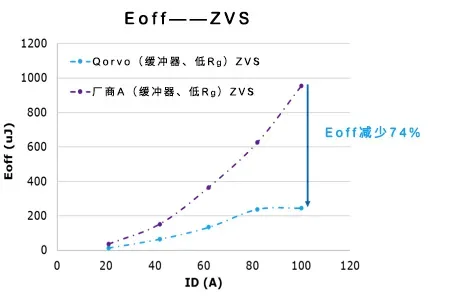

圖3,E1B模塊在VDS = 800V、IDS = 100A時的關斷波形:(a)Qorvo UHB100SC12E1BC3-N(1,200V、100A E1B模塊),帶緩沖器(660pF、4.7Ω、Rgoff 2.2Ω);(b)廠商A的1,200V 100A模塊,帶緩沖器(660pF、4.7Ω、Rgoff 2.2Ω),(c)廠商A的1,200V 100A模塊,不帶緩沖器(Rgoff 5Ω)

圖4,在VDS = 800V、IDS = 100A條件下,E1B模塊關斷開關損耗的DPT測試結果:(a)廠商A的1,200V 100A模塊,帶緩沖器(660pF、4.7Ω、Rgoff 2.2Ω)和不帶緩沖器(Rgoff 5Ω)的對比;(b)Qorvo UHB100SC12E1BC3-N(1,200V、100A E1B模塊),帶緩沖器(660pF、4.7Ω、Rgoff 2.2Ω),和廠商A帶緩沖器模塊(660pF、4.7Ω、Rgoff 2.2Ω)的對比

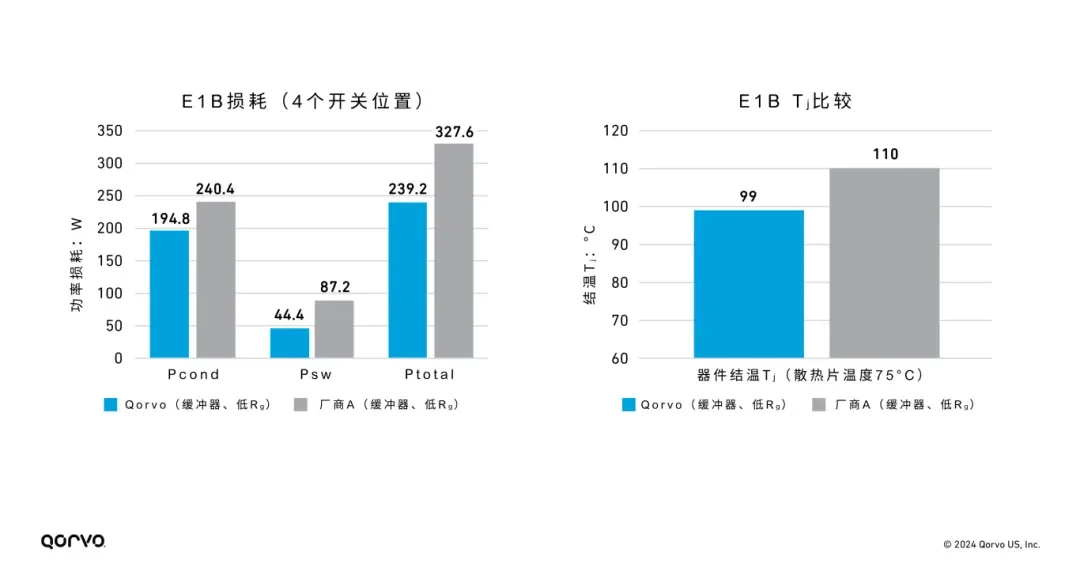

一項以800V母線電壓和100A負載電流進行的雙脈沖測試表明,為廠商A的SiC MOSFET模塊添加緩沖器后,損耗迅速降低了50%。而結合使用Qorvo基于JFET的器件與緩沖器,可使關斷開關損耗進一步降低74%。這使得開關速率得以提高三倍,并推動外部無源組件尺寸的減小。以圖5所示的50kW PSFB(相移全橋)仿真為例,關斷開關損耗減少74%使得結溫相應降低10%。最終,更佳的熱性能帶來更小的散熱片和冷卻結構;兩者的結合,共同實現了轉換器體積的縮減。

圖5,50kW移相全橋FET損耗仿真;應用條件:50kW、800V Vin、

400V Vout、150kHz、死區時間150ns、散熱器溫度75°C

盡管軟開關技術有諸多復雜性,但SiC技術為其優化使用創造了機會。對于需要高效率和高密度的設計,則可以跳出基于MOSFET經典結構的束縛來實現其目標。

本文作者

Qorvo 高級產品應用工程師

Mike Zhu于2015年獲得美國俄亥俄州立大學電氣與計算機工程碩士學位,在SiC和GaN器件評估,高頻、高功率密度的功率器件設計以及寬帶隙器件的EMI解決方案方面擁有10年以上的研究經驗。

原文始發于微信公眾號(Qorvo Power):Qorvo E1B SiC模塊:成就高效功率轉換系統的秘密武器