點擊藍字 關注我們

全文刊載于《前瞻科技》2022年第3期"集成電路科學與工程專刊”,點擊文末“閱讀原文”獲取全文。

曹立強

-研究員

-博士研究生導師

-中國科學院微電子研究所副所長

侯峰澤(通信作者)

-副研究員

近年來,先進封裝技術的內驅力已從高端智能手機領域演變為高性能計算和人工智能等領域,涉及高性能處理器、存儲器、人工智能訓練和推理等。當前集成電路的發展受“四堵墻”(“存儲墻”“面積墻”“功耗墻”和“功能墻”)制約,以芯粒(Chiplet)異質集成為核心的先進封裝技術,將成為集成電路發展的關鍵路徑和突破口。文章概述近年來國際上具有“里程碑”意義的先進封裝技術,闡述中國大陸先進封裝領域發展的現狀與優勢,分析中國大陸先進封裝關鍵技術與世界先進水平的差距,最后對未來中國大陸先進封裝發展提出建議。

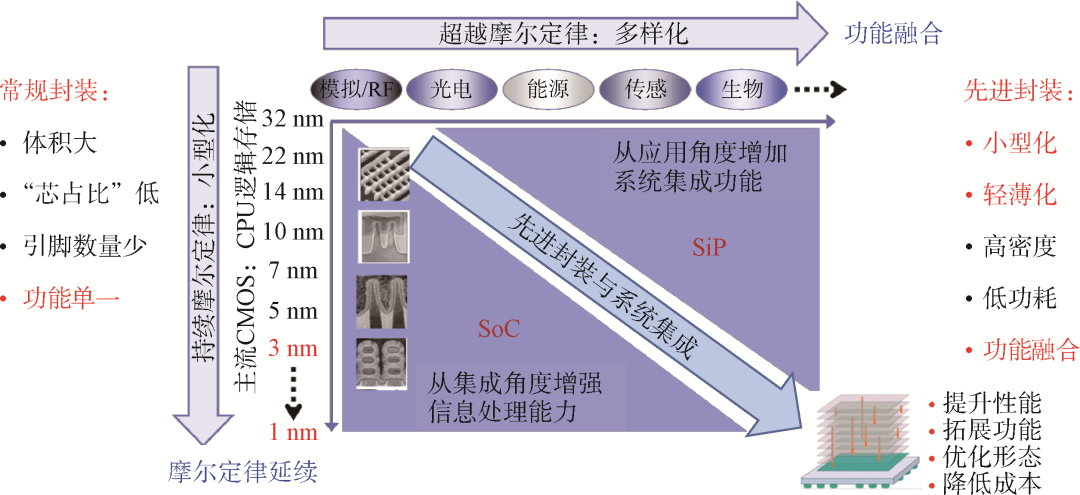

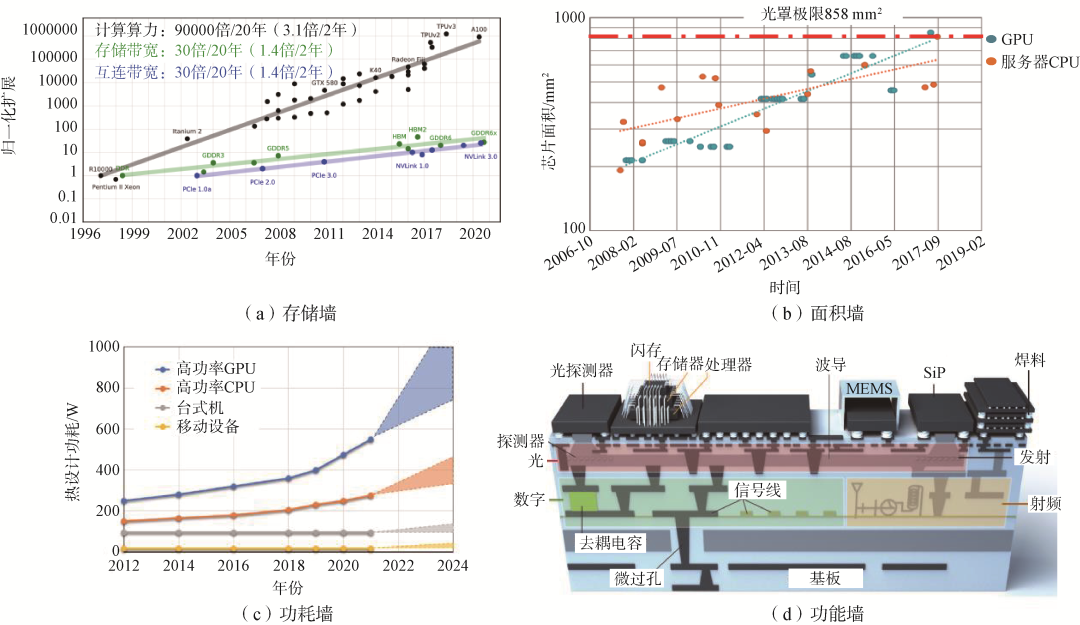

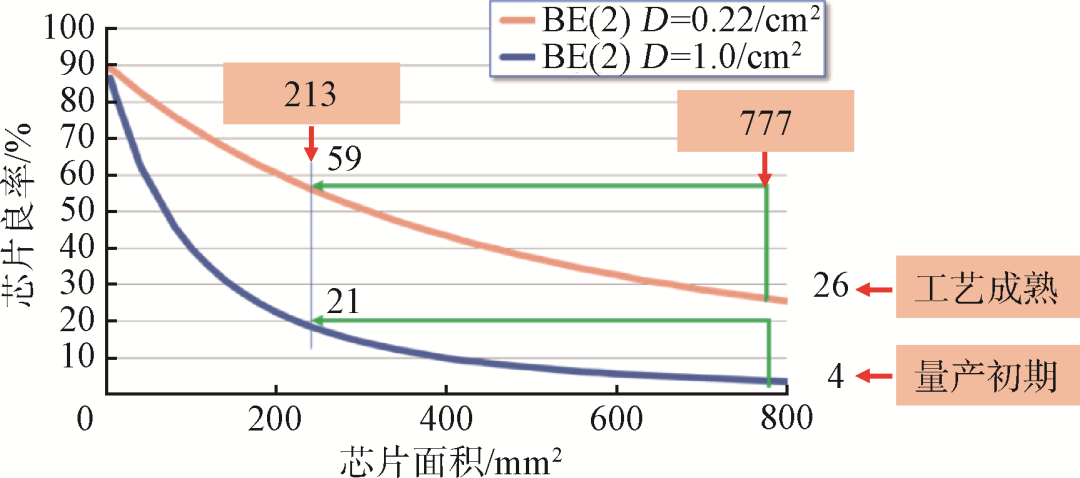

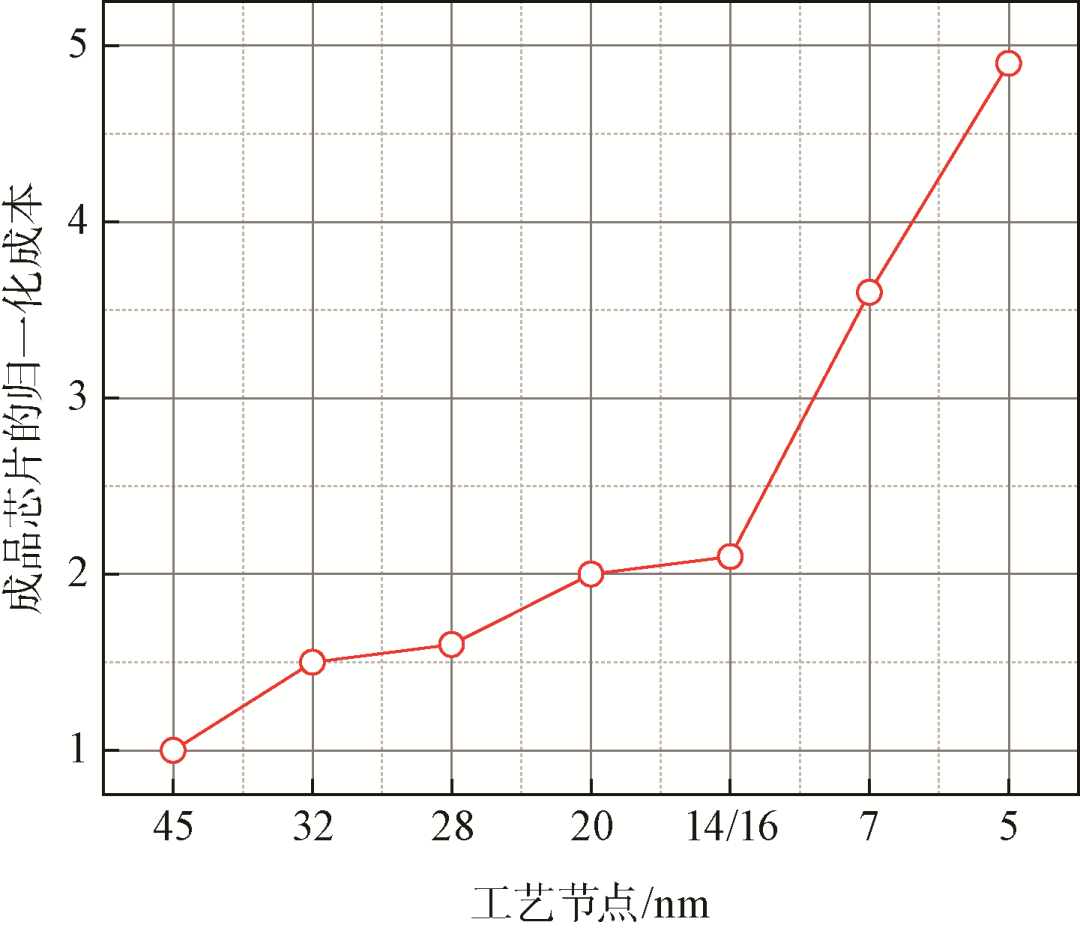

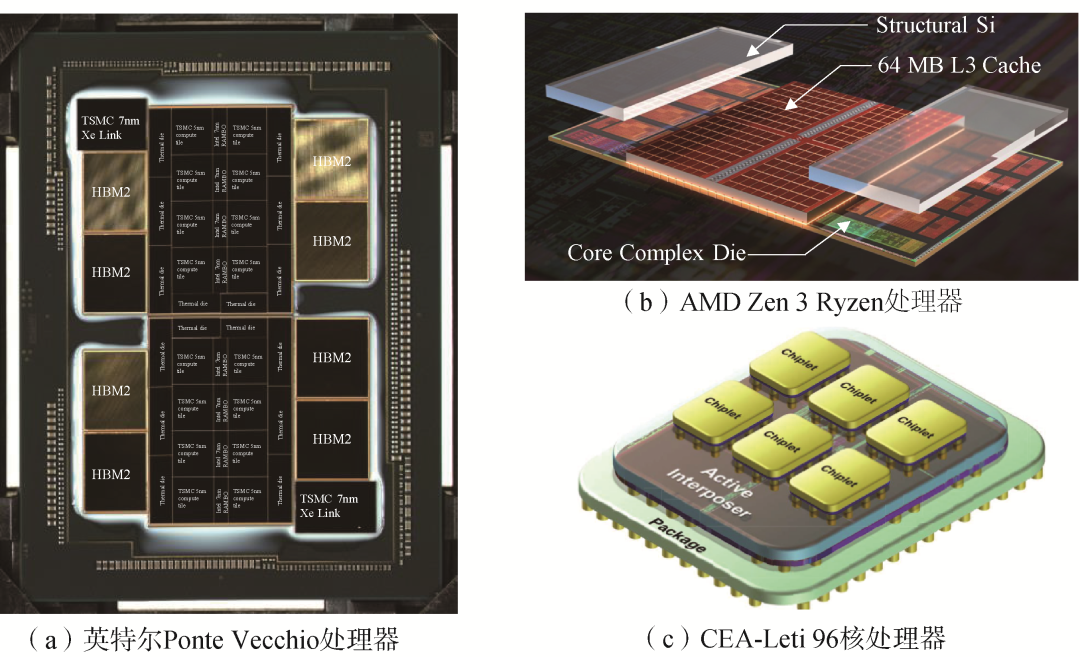

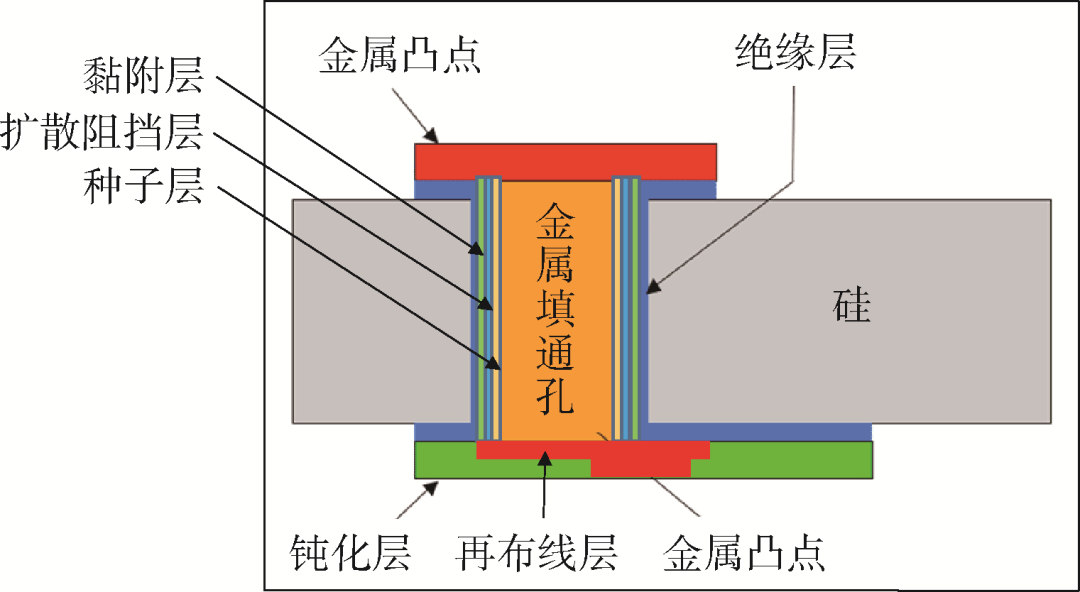

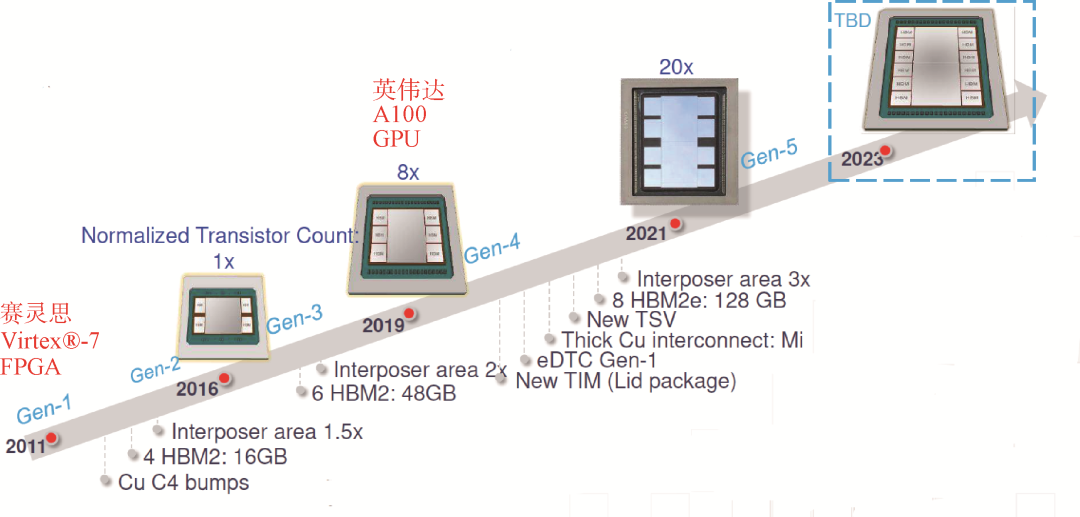

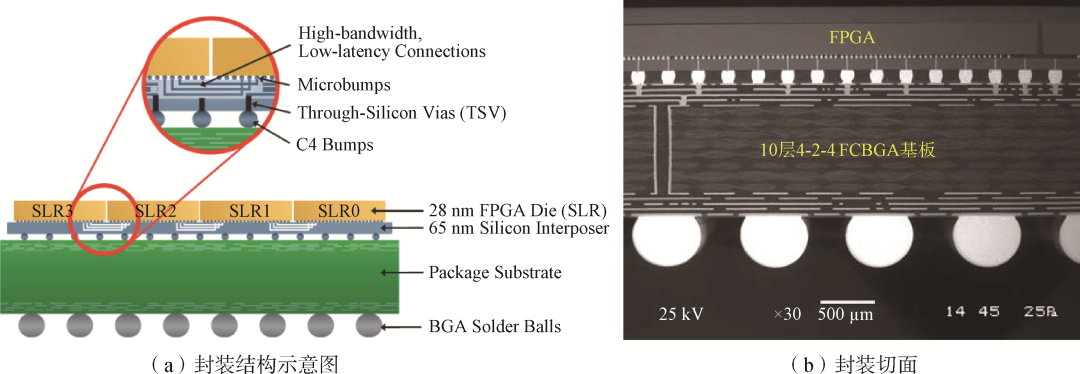

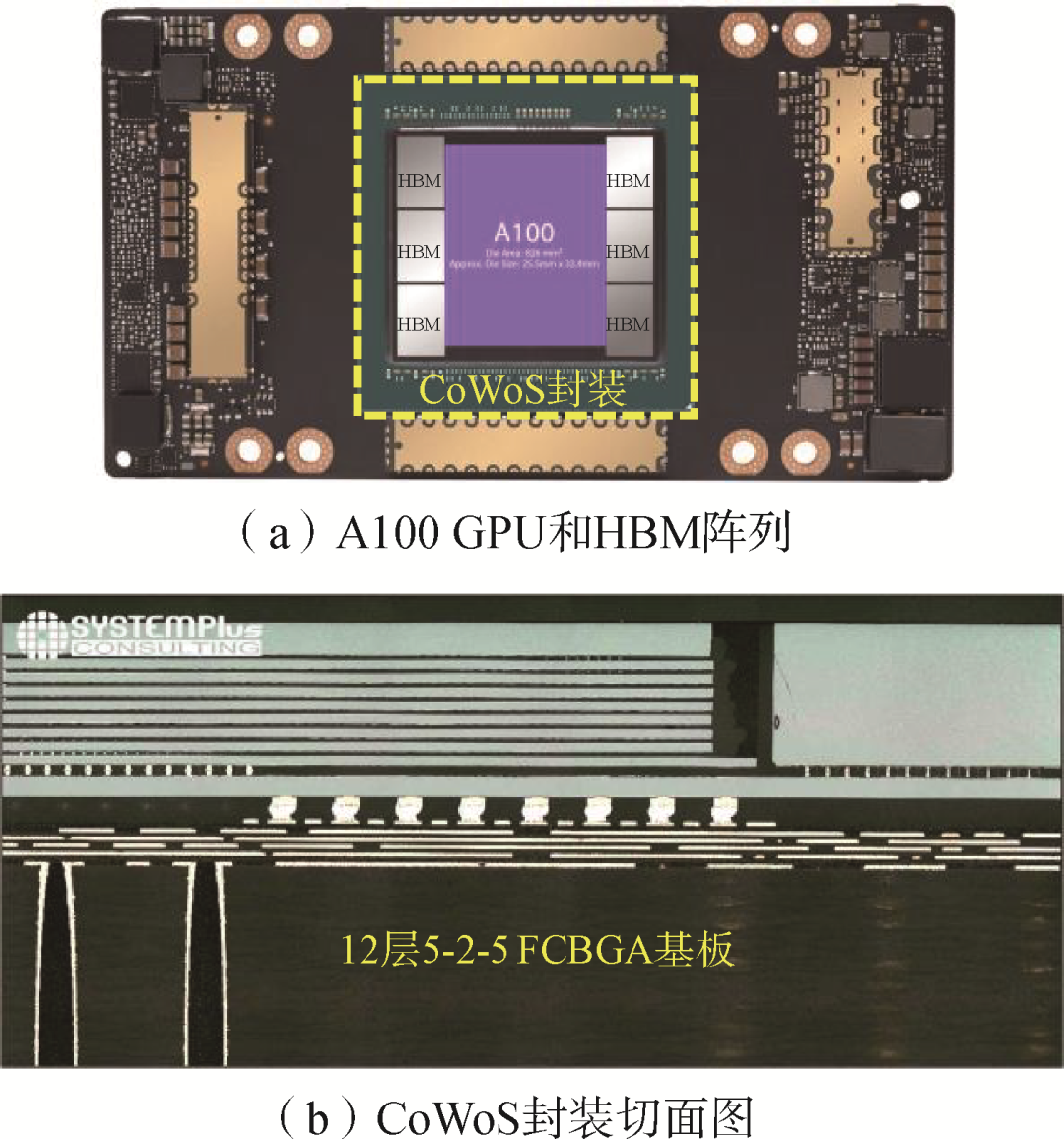

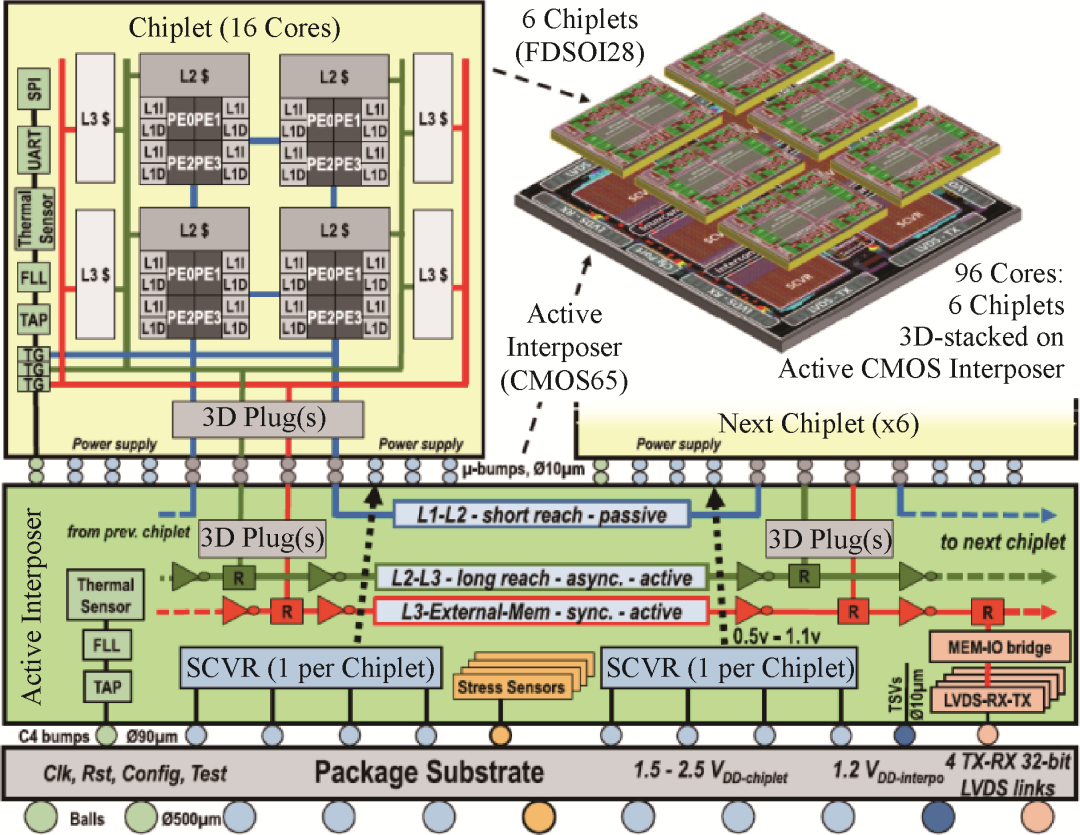

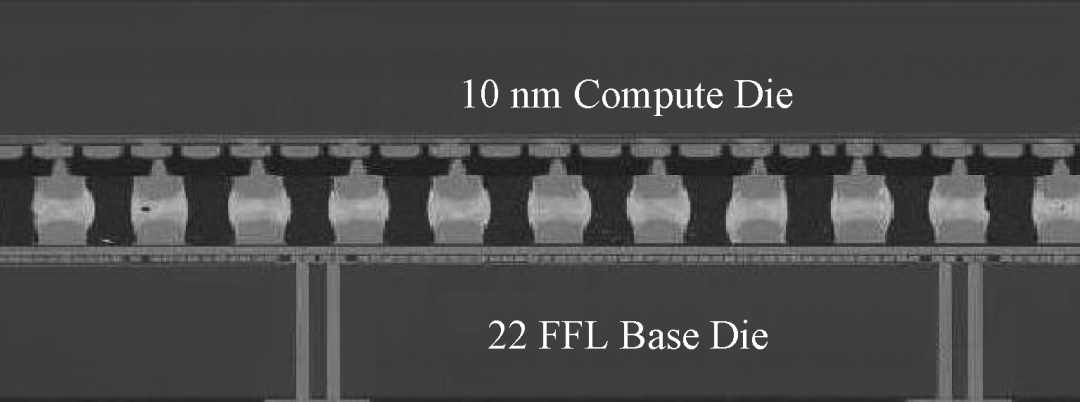

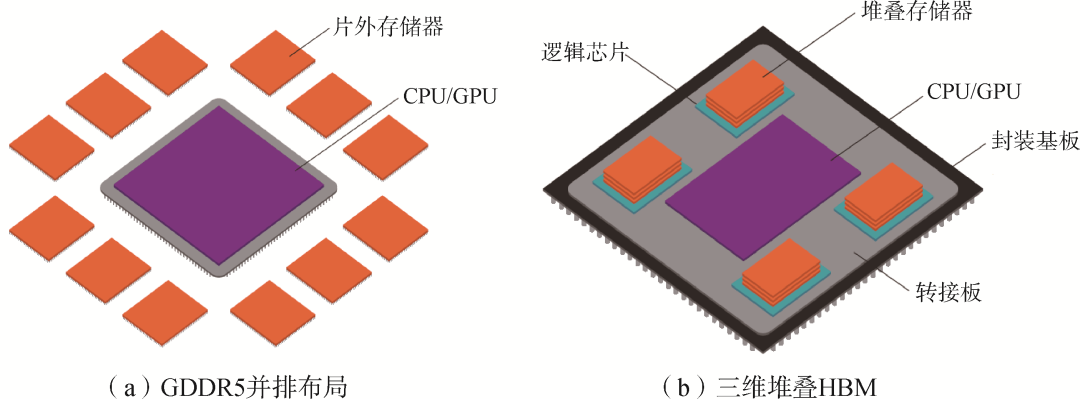

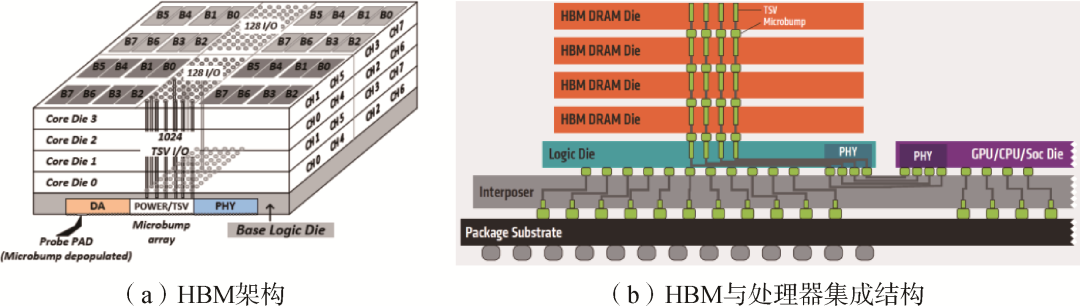

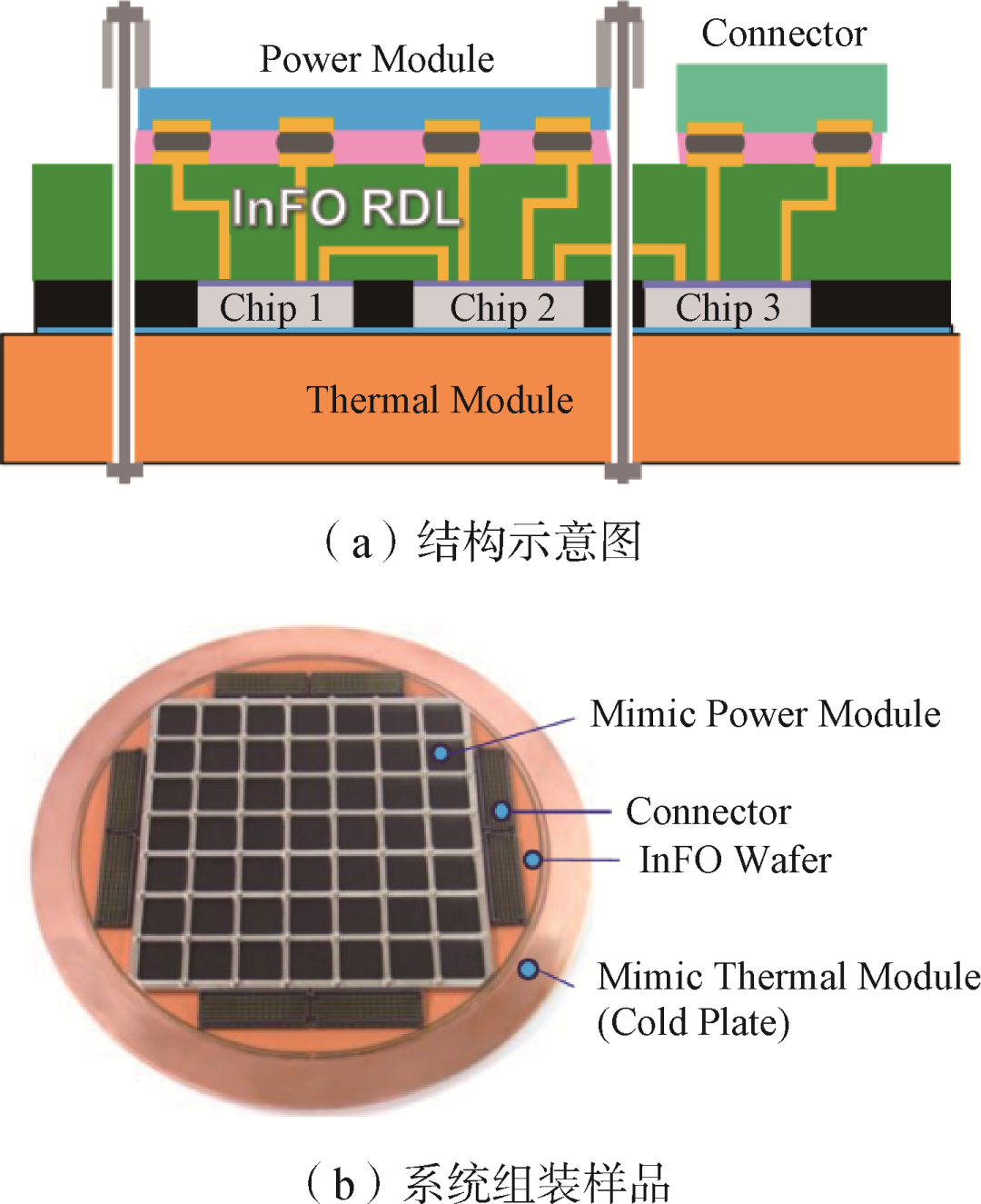

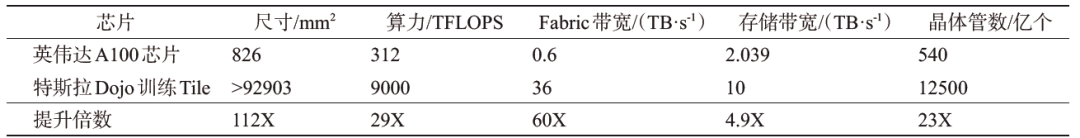

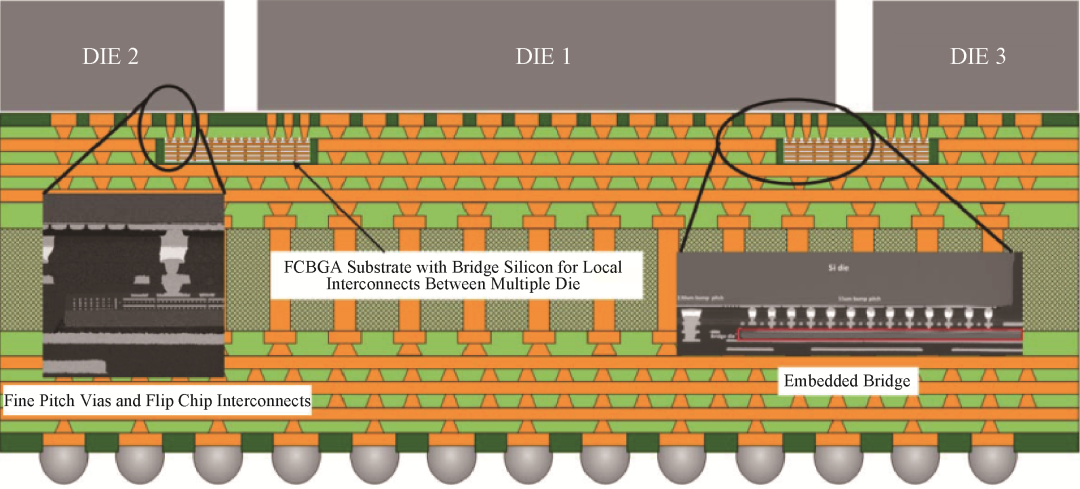

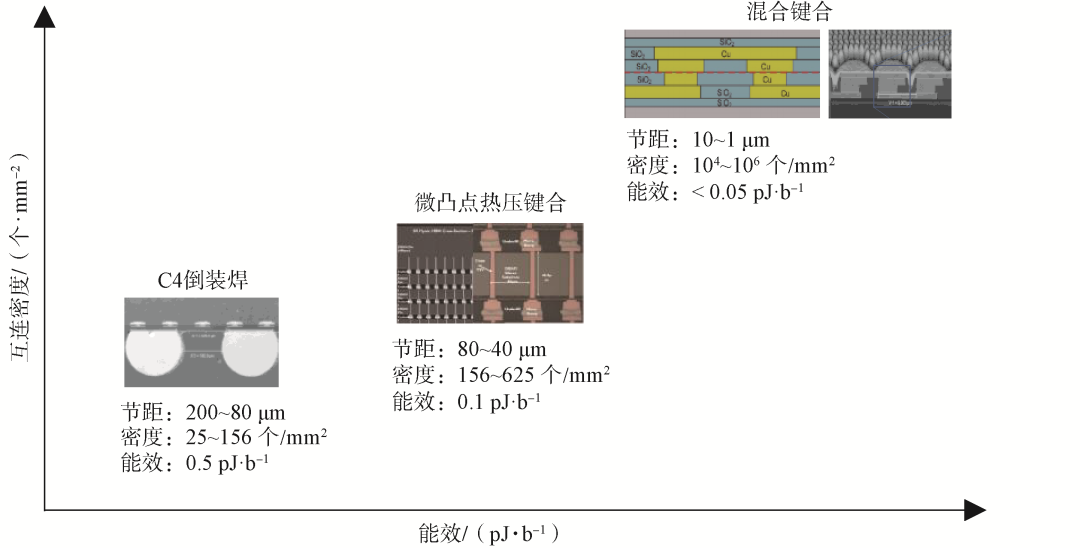

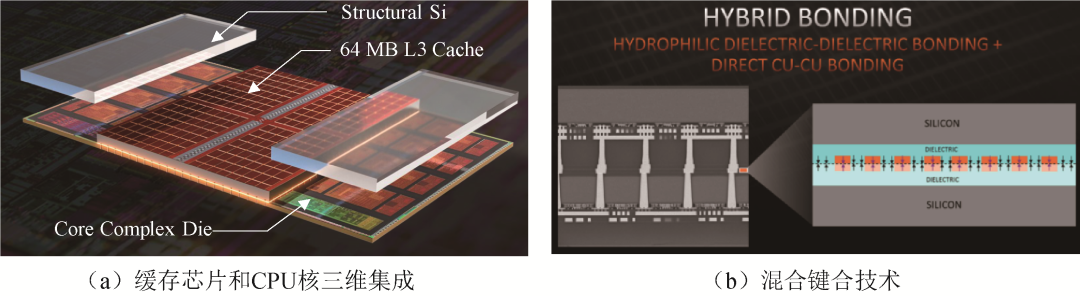

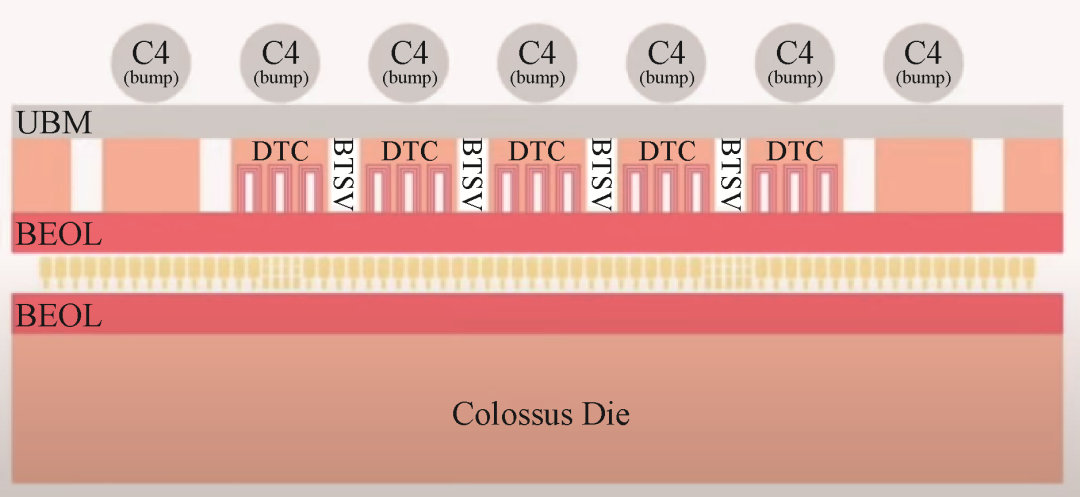

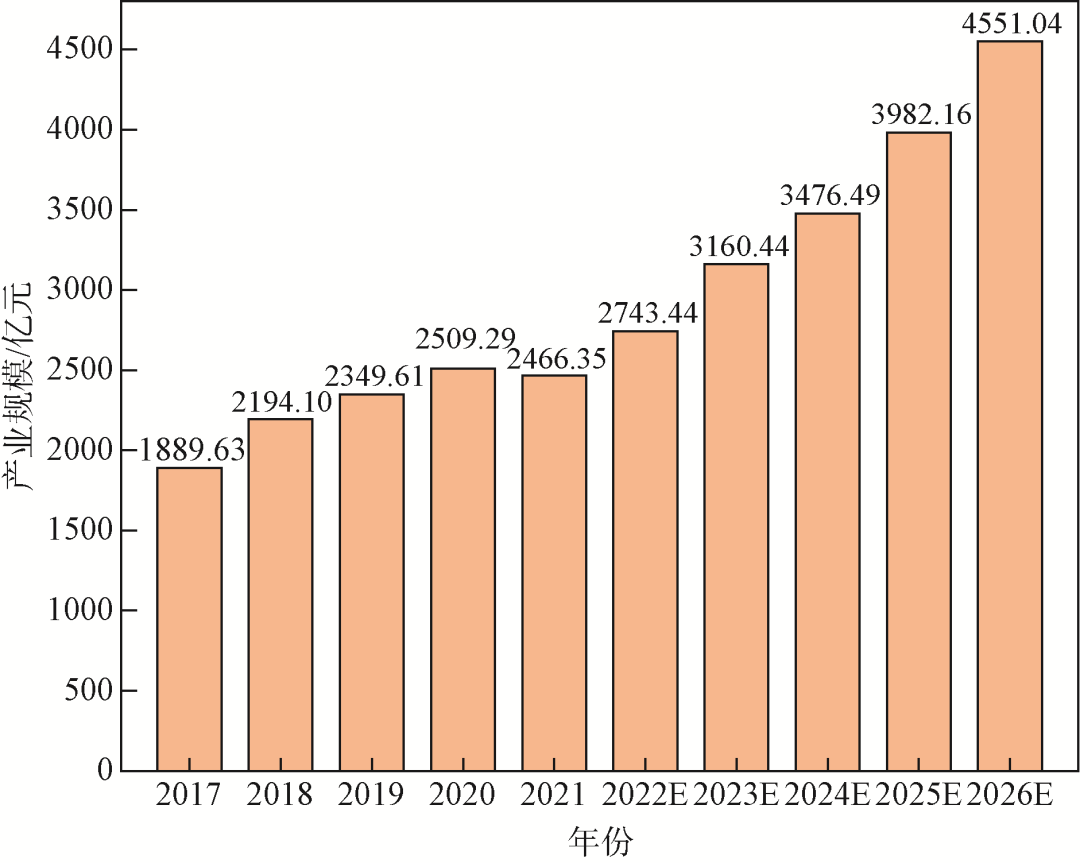

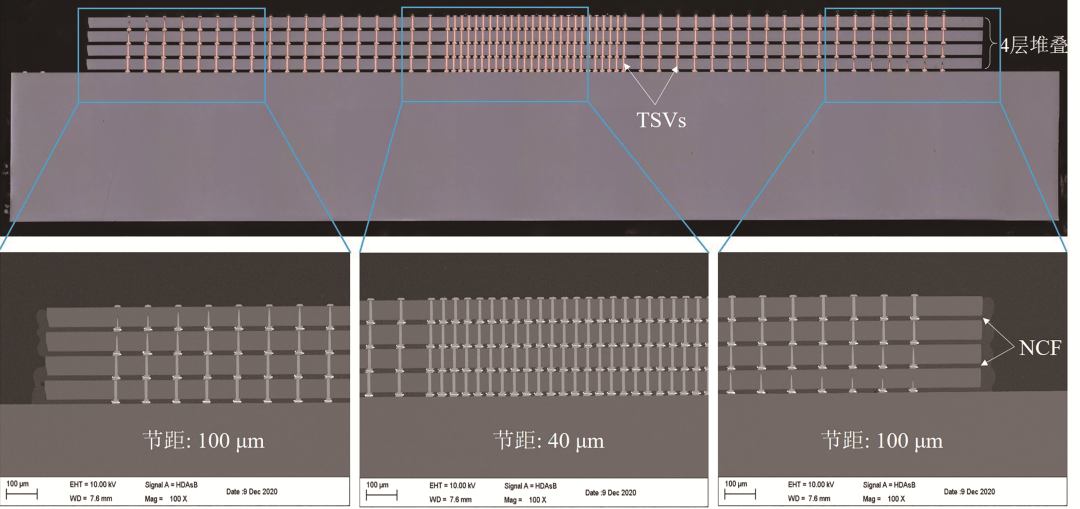

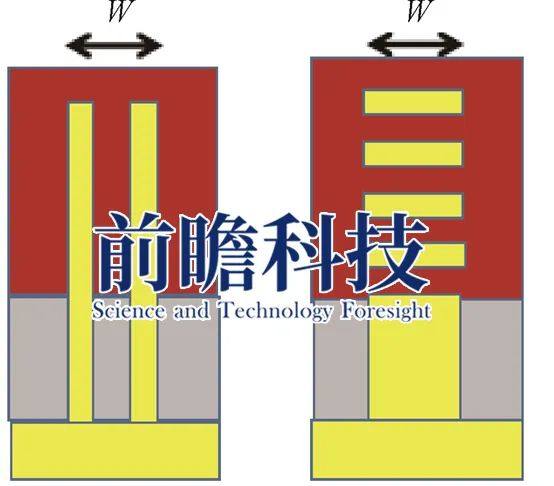

集成電路是國之重器,設計、制造和封裝是集成電路產業發展的三大支柱;封裝是芯片實用化的起點,是溝通芯片內部世界與外部系統的橋梁。集成電路沿著兩條技術路線發展(圖1),一條是持續摩爾定律,向小型化方向發展,即通過微縮互補金屬氧化物半導體(Complementary Metal- Oxide-Semiconductor, CMOS)器件的晶體管柵極尺寸增加芯片晶體管數量,從而提升芯片的性能。到目前為止,工藝制程已發展至5 nm節點,主要產品為圖像處理器(GPU)和中央處理器(CPU),全世界只有中國臺灣積體電路制造股份有限公司(簡稱臺積電)、美國英特爾和韓國三星等公司具備10 nm及以下節點的制造能力。另一條是超越摩爾定律,向多樣化方向發展,即采用先進的封裝技術將處理、模擬/射頻(Radio Frequency, RF)、光電、能源、傳感、生物等集成在一個系統內,進行系統級封裝(System in Package, SiP),實現系統性能的提升。相比常規封裝,先進封裝具有小型化、輕薄化、高密度、低功耗和功能融合等優點,不僅可以提升性能、拓展功能、優化形態,相比系統級芯片(System on Chip, SoC),還可以降低成本。 圖1 集成電路發展路線圖 先進封裝技術發展特點 封裝技術的發展史是芯片性能不斷提高、系統不斷小型化的歷史,大致分為4個階段:第1階段(1970年前),直插型封裝,以雙列直插封裝(Dual In-line Package, DIP)為主;第2階段(1970—1990年),以表面貼裝技術衍生出的小外形封裝(Small Outline Package, SOP)、J型引腳小外形封裝(Small Outline J-leaded, SOJ)、無引腳芯片載體(Leadless Chip Carrier, LCC)、扁平方形封裝(Quad Flat Package, QFP)4大封裝技術和針柵陣列(Pin Grid Array, PGA)技術為主;第3階段(1990—2000年),球柵陣列(Ball Grid Array, BGA)、芯片尺寸封裝(Chip Scale Package, CSP)、倒裝芯片(Flip-Chip, FC)封裝等先進封裝技術開始興起;第4階段(2000年至今),從二維封裝向三維封裝發展,出現了晶圓級封裝(Wafer Level Package, WLP)、系統級封裝、扇出型(Fan-Out, FO)封裝、2.5D/3D封裝、嵌入式多芯片互連橋接(Embedded Multi-die Interconnect Bridge, EMIB)等先進封裝技術。 近年來,先進封裝技術的內驅力已從高端智能手機領域演變為高性能計算和人工智能等領域,涉及高性能處理器、存儲器、人工智能訓練和推理等。 當前,除了傳統委外封測代工廠(OSAT)和科研機構做封裝外,晶圓代工廠(Foundry)、整合元器件制造商(IDM)、無廠半導體公司(Fabless)、原始設備制造商(OEM)都在大力發展先進封裝或相關關鍵技術。目前臺積電已成為先進封裝技術創新的引領者之一,相繼推出了基板上晶圓上的芯片(Chip on Wafer on Substrate, CoWoS)封裝、整合扇出型(Integrated Fan-Out, InFO)封裝、系統整合芯片(System on Integrated Chips, SoIC)等;英特爾推出了EMIB、Foveros和Co-EMIB等先進封裝技術,力圖通過2.5D、3D和埋入式3種異質集成形式實現互連帶寬倍增與功耗減半的目標;三星電子推出了扇出型面板級封裝(Fan-Out Panel Level Package, FOPLP)技術,在大面積的扇出型封裝上進一步降低封裝體的剖面高度、增強互連帶寬、壓縮單位面積成本,取得性價比的優勢。 當前集成電路的發展受“存儲墻”“面積墻”“功耗墻”和“功能墻”這“四堵墻”的制約。如圖2(a)。所示,處理器的峰值算力每兩年增長3.1倍,而動態存儲器的帶寬每兩年增長1.4倍,存儲器的發展速度遠落后于處理器,相差1.7倍。為了突破“存儲墻”,業界提出了存內計算和近存計算兩種技術途徑,其中存內計算的能效高、精度低;近存計算的算力高、精度高,它是一種基于先進封裝的技術途徑,通過超短互連技術,可實現存儲器和處理器之間數據的近距離搬運。 圖2 集成電路發展面臨的挑戰 當芯片制程相同時,通過增大芯片面積可以集成更多的晶體管數量,從而提升芯片的性能,然而,芯片尺寸受限于光刻機的光罩極限,如圖2(b)所示,當前最先進的極紫外光刻機的最大光罩面積為858 mm2(26 mm×33 mm)。2020年,美國英偉達公司發布了A100 GPU芯片,采用臺積電7 nm鰭式場效應晶體管(Fin Field-Effect Transistor, FinFET)工藝,通過常規手段制造了接近1個光罩面積的芯片,面積達826 mm2(~25.5 mm×32.4 mm),擁有540億個晶體管,單精度(FP32)算力高達19.5 TFLOPS,存儲帶寬為2.039 TB/s。2019年,美國人工智能初創公司Cerebras System通過臺積電芯片間連接技術(Cross-die Wires)推出了世界上最大的芯片,面積達到46225 mm2(215 mm×215 mm),約等于A100的56倍,存儲帶寬達20 PB/s,該技術雖突破了1個光罩面積,但成本極高。當前,通過先進封裝技術集成多顆芯片是突破芯片“面積墻”的一種低成本主流方案。 如圖2(c)所示,近年來單個GPU和CPU的熱設計功耗(Thermal Design Power, TDP)逐年增大。2024年單個GPU的TDP將突破千瓦級,由多個GPU芯片和高帶寬存儲器(High Bandwidth Memory, HBM)陣列組成的系統,TDP可能突破萬瓦級,熱設計者將面臨極大的挑戰,為突破“功耗墻”,迫切需要采用更先進的冷卻技術。 單一襯底可實現的功能有限,為突破“功能墻”,可通過多芯片異質集成技術,將傳感、存儲、計算、通信等不同功能的元器件集成在一起,實現電、磁、熱、力等多物理場的有效融合,如圖2(d)所示。 先進封裝技術研究進展 以芯粒(Chiplet,又稱小芯片)異質集成為核心的先進封裝技術,將成為集成電路發展的關鍵路徑和突破口。本節將介紹與芯粒相關的先進封裝技術研究進展,包括芯粒異質集成技術和典型先進封裝技術兩部分。 2.1? 芯粒異質集成技術 增大芯片尺寸可增多晶體管數量,從而可以集成更復雜的微體系結構、更多的片上存儲器以及更多的內核,提高芯片性能。然而,芯片尺寸受限于光罩極限,且芯片良率隨尺寸的增大而降低。如圖3所示,工藝成熟后,當芯片面積從213 mm2增至777 mm2時,良率降低了33%,因此,芯片的成本隨尺寸的增大而增加,芯粒異質集成技術已成為維持摩爾定律和超越光罩極限的一種有效方法。 圖3 芯片良率與芯片面積的關系 采用更先進的制程也可提升芯片的性能。然而,隨著工藝節點向小微縮,采用先進制程制造大芯片的成本越來越高,如圖4所示。相比采用45 nm節點制造的250 mm2的芯片,采用16 nm工藝節點后,芯片每平方毫米的成本增加1倍以上,采用5 nm工藝后,成本將增加4~5倍,因此摩爾定律已從單個晶體管微縮向系統級微縮演變。芯粒是一種有效的片間互連和封裝架構,即將大芯片拆分成多顆芯粒,以搭積木的形式將不同功能、不同合適工藝節點制造的芯粒封裝在一起。拆解后的小芯片可形成貨架產品,便于快速靈活的開發,降低開發成本與周期的同時,化整為零,極大減少了知識產權(Intellectual Property, IP)問題。同時,多種芯片的靈活集成可有效提高產品的功能性,利用常規工藝即可實現先進的集成芯片性能,從而以全新的角度解決先進制程技術局限導致的技術代際落后問題,形成芯粒異質集成的差異化競爭。 圖4 芯片成本隨工藝節點微縮遞增 2017年8月美國國防部高級研究計劃局(DARPA)的“電子復興計劃”中,正式發布了“通用異質集成和知識產權復用策略”項目(CHIPS),其目標是促成一個兼容、模塊化、IP復用的芯粒生態系統,DARPA整合了軍工企業、半導體企業、電子設計自動化(Electronic Design Automation, EDA)企業以及高校共同推進此項目。近年來,美國英特爾、AMD和法國原子能委員會電子與信息技術實驗室(CEA-Leti)分別推出了Ponte Vecchio處理器、Zen 3 Ryzen處理器和96核處理器等芯粒產品,如圖5所示。其中,Ponte Vecchio處理器集成了47個功能單元和16個散熱單元,Zen 3 Ryzen處理器實現了CPU核和三級靜態緩存的三維垂直堆疊,96核處理器集成了6個相同的計算芯粒。 圖5 典型芯粒產品 2014年9月華為開發了首款全功能的基于臺積電16 nm FinFET工藝的網絡處理器,通過CoWoS封裝技術集成了1個16 nm 32核ARM Cortex-A57、1顆28 nm邏輯芯片和1顆28 nm輸入/輸出(I/O)芯片,相比上一代產品,性能提升了3倍。 2.2? 典型先進封裝技術 芯粒異質集成涉及的典型先進封裝技術包括硅通孔(Through Silicon Via, TSV)、超高密扇出、EMIB以及混合鍵合等。 2.2.1? 硅通孔技術 TSV是一種垂直互連技術,它是由威廉·肖克利(William Shockley)于1958年提出的,目前應用最廣泛的填銅TSV,由日本超級先鋒協會首創電子技術聯盟(1999—2003年)率先實現。國際半導體技術路線藍圖將TSV定義為連接硅晶圓兩面并與硅襯底和其他通孔絕緣的電互連結構,其基本結構示意圖如圖6所示,TSV的尺寸多為10 μm×100 μm和30 μm×200 μm,開口率介于0.1%~1%。相比平面互連,TSV可減小互連長度和信號延遲,降低寄生電容和電感,實現芯片間的低功耗和高速通信,增加寬帶和實現封裝小型化。當前TSV主要用于硅轉接板、芯片三維堆疊等方面。其中,硅轉接板作為芯片和有機基板的中間層,因與硅芯片的熱膨脹系數相同,在硅轉接板上可集成多顆具有高密度凸點的芯片,如美國賽靈思的現場可編程門陣列(Field-Programmable Gate Array, FPGA)產品;可作為HBM和處理器的互連通道,如英偉達A100產品;可實現兩顆SoC芯片的拼接,如蘋果最新發布的M1 Ultra芯片。硅轉接板以是否集成特定功能分為無源和有源轉接板,無源轉接板僅包含金屬互連層,有源轉接板包含可集成供電、片內網絡通信等功能。芯片三維堆疊技術可通過TSV實現多芯片的短距離高速通信,HBM就是一種典型的應用。 圖6 TSV基本結構示意圖 1)無源轉接板技術 臺積電的CoWoS是一項2.5D封裝技術,采用的是無源轉接板,其主要工藝特點如下:①通過微凸點將多顆芯片并排鍵合至硅基無源轉接板晶圓上,形成芯片至晶圓(Chip on Wafer, CoW)裝配體;②減薄晶圓背面以露出TSV;③制備可控塌陷芯片連接(C4)凸點;④切割晶圓并將切好的晶圓倒裝焊至封裝基板(Substrate)上,形成最終的CoWoS封裝。 圖7為臺積電CoWoS封裝技術路線。自2012年起,該技術已發展5代,通過掩膜版拼接技術,無源轉接板尺寸從接近1個光罩面積增至3個光罩面積(2500 mm2)。前兩代為同質芯片集成,主要集成硅基邏輯芯片,從第3代起演變為異質芯片集成,主要集成邏輯SoC芯片和HBM陣列。為提高芯片的電源完整性,其開始在無源轉接板內集成深溝槽電容。 圖7 臺積電CoWoS封裝技術路線 2011年,賽靈思推出了當時世界上最大的FPGA產品。為了解決大芯片良率低的問題,該公司采用臺積電的第1代CoWoS封裝技術(圖8),將4顆28 nm FPGA小芯片組裝在1個100 μm厚采用65 nm工藝制造的無源轉接板上,每顆芯粒的尺寸為7 mm×12 mm,硅轉接板尺寸為25 mm×31 mm,接近1個光罩面積,基板為10層FCBGA基板,尺寸為42.5 mm×42.5 mm。 圖8 賽靈思FPGA CoWoS封裝 2020年,英偉達采用臺積電第4代CoWoS技術封裝了其A100 GPU系列產品(圖9(a)),將1顆英偉達A100 GPU芯片和6個三星電子的HBM2集成在一個1700 mm2的無源轉接板上,每個HBM2集成1顆邏輯芯片和8個動態隨機存取存儲器(DRAM),基板為12層倒裝芯片球柵格陣列(Flip-Chip Ball Grid Array, FCBGA)基板(圖9(b)),尺寸為55 mm×55 mm。 圖9 英偉達A100 GPU CoWoS封裝 2)有源轉接板技術 有源轉接板是無源轉接板的技術延伸,在無源轉接板內部集成一些功能單元。法國CEA-Leti開發了一款基于65 nm CMOS工藝的有源轉接板,面積約200 mm2,擁有1500萬個晶體管,7層金屬,集成了可近距離直接給芯片供電的開關式電容電壓調節器(Switching Capacitor Voltage Regulator, SCVR)、片間通信的分布式片上網絡、片外通信的系統I/O以及可測性設計(Design For Test, DFT)等功能。采用20 μm間距的微凸點,將6個基于28 nm全耗盡型絕緣體上硅(Fully Depleted Silicon-On-Insulator, FDSOI)工藝的計算芯粒和一個基于65 nm CMOS工藝的有源轉接板面對面熱壓鍵合在一起,每顆芯粒的面積為22.4 mm2,擁有3.95億個晶體管,16核,集成后總共有96核,實現了220 GOPS的系統算力,電壓轉換效率為82%,芯片間互連帶寬密度為3 Tb/(s·mm-2),能效為0.59 pJ/b(圖10)。英特爾開發了一款基于22 nm工藝的有源轉接板,包含11層金屬和TSV,TSV與頂部金屬層相鄰,面積為90.85 mm2,集成了供電、PCIe Gen3、USB Type C等功能。通過Foveros技術將基于10 nm FinFET先進工藝的計算芯片和22 nm成熟工藝的有源轉接板面對面連接在一起,如圖11所示。其中,計算芯片有13層金屬,面積為82.5 mm2,融合了混合CPU架構、圖像等功能。 圖10 CEA-Leti 96核處理器集成技術 圖11 英特爾Foveros技術 3)HBM技術 如前所述,存儲器的“存儲墻”限制了計算芯片性能的發揮,第5版圖形用雙倍數據傳輸率存儲器(GDDR5)的帶寬極限為32 GB/s,由邏輯芯片和多層DRAM堆疊而成的HBM技術突破了帶寬瓶頸,HBM1和HBM2的帶寬分別為128 GB/s和256 GB/s,未來HBM3可突破1.075 TB/s。當片外存儲從并排布局圖形用雙倍數據傳輸率(Graphics Double Data Rate, GDDR)存儲器轉為三維堆疊HBM,容量為1 GB時,HBM模組占用面積減少94%,如圖12(a)和圖12(b)所示。第1代HBM的架構如圖13(a)所示,由邏輯芯片和4層DRAM堆疊在一起,每個HBM有8個通道,每個通道有128個I/O,因此每個HBM有1024個I/O,即1024個TSV,位于HBM的中間區域。存儲器和處理器通過無源轉接板上的再布線層(Re-Distributed Layer, RDL)將HBM邏輯芯片的端口物理層(Port Physical Layer, PHY)與處理器的PHY連接在一起,如圖13(b)所示。 圖12 片外存儲從并排布局轉為三維堆疊 圖13 HBM架構和封裝集成示意圖 2.2.2? 超高密度扇出技術 2020年,臺積電發布了一種超高密度扇出封裝技術,即集成扇出型晶圓上系統(InFO_SoW),如圖14所示,通過超高密度扇出封裝技術將多顆好的晶粒(Known Good Die, KGD)、供電、散熱模塊和連接器緊湊地集成在晶圓上,包含6層RDL,前3層線寬/線距為5/5 μm,用于細線路芯片間互連;后3層線寬/線距為15/20 μm,用于供電和連接器互連。相比印制電路板(Printed Circuit Board, PCB)級多芯片模塊,InFO_SoW具有高帶寬、低延遲和低功耗的特點。 圖14 臺積電InFO_SoW技術 2021年8月19日,特斯拉人工智能(Artificial Intelligence, AI)日推出了其自研的面向AI專用領域的Dojo D1芯片,如圖15(a)所示。D1芯片采用臺積電7 nm工藝,面積為645 mm2,晶體管數量達500億個,1 mm2面積上的晶體管數量已超過英偉達A100芯片,包含354個訓練節點,BF16/CFP8的峰值算力高達362 TFLOPS,TDP為400 W。通過臺積電InFO_SoW封裝技術將25顆D1芯片集成在一起,再將供電、散熱、連接器等模塊集成進來,形成1個Dojo訓練Tile,BF16/CFP8算力高達9.1 PFLOPS,如圖15(b)所示。將120個Dojo訓練Tile組裝成了ExaPOD超級計算機,ExaPOD含有3000顆D1芯片,106.2萬個訓練節點,BF16/CFP8算力可以達到1.1 EFLOPS。表1對比了英偉達A100芯片與特斯拉Dojo訓練Tile的主要性能指標。從表1中可以看出,晶圓級片上大規模集成可大幅提升系統算力和帶寬,是提升系統能力的一種重要途徑。 圖15 特斯拉Dojo D1芯片晶圓級片上大規模集成 表1 英偉達A100芯片與特斯拉Dojo訓練Tile主要性能指標對比 2.2.3? EMIB技術 EMIB技術最早由英特爾的Mahajan和Sane于2008年提出,后又經Braunisch和Starkston等改進,近年來已發展成為英特爾最具代表性的先進封裝技術之一,已用于其多款FPGA產品,如Agilex FPGA和Direct RF FPGA。它是在有機基板中埋入若干超薄的(厚度一般小于100 μm)、高密度的硅橋,實現兩兩芯片間的互連,如圖16所示。目前英特爾可量產的硅橋尺寸為2 mm×2 mm~12 mm×12 mm,包含4層RDL和1層焊盤,線寬/線距為1 μm/1 μm。EMIB可提供芯片間局部高密度互連,可靈活地放置在基板任意需要互連的地方,不限制芯片的集成數量與位置,不影響基板上其他線路的布局布線。 圖16 英特爾EMIB互連技術 2.2.4? 混合鍵合技術 圖17為鍵合技術的演進,其中混合鍵合是通過銅—銅金屬鍵合和二氧化硅—二氧化硅介質層鍵合實現無凸點永久鍵合的芯片三維堆疊高密度互連技術,可實現極小間距的芯片焊盤互連,每平方毫米可互連的芯片焊盤數為104~106個,可以提供更高的互連密度、更小更簡單的電路、更大的帶寬、更小的電容和更低的功耗。與傳統C4焊點和微凸點連接技術相比,混合鍵合技術的主要優點有:①實現芯片之間無凸點互連,微凸點的取消將進一步降低芯片之間通道的寄生電感和信號延時;②實現芯片之間超細間距的互連,比微凸點提高10倍以上,超細間距的互連將增加布線有效使用面積,大幅增加通道數量,實現數據處理串并轉換,簡化I/O端口電路,增大帶寬;③實現超薄芯片制備,通過芯片減薄可使芯片厚度和重量大幅降低,并且可進一步提升系統中芯片的互連帶寬;④實現鍵合可靠性的提高,銅—銅觸點間以分子尺度融合,取消了焊料連接,二氧化硅—二氧化硅以分子共價鍵鍵合取消了底填材料,極大提高了界面鍵合強度,增強了芯片的環境適應性。 圖17 鍵合技術的演進 美國AMD通過混合鍵合技術將兩個64 MB三級靜態緩存芯片和1個含TSV的8核CPU垂直鍵合在一起,實現了3D芯粒,如圖18所示,其混合鍵合的間距為9 μm,互連密度約12345個/mm2,相比間距為36 μm的微凸點,互連密度提升大于15倍,互連能效提升大于3倍。 圖18 AMD 3D芯粒技術 2022年3月,英國AI芯片公司Graphcore發布了一款智能處理單元(Intelligent Processing Unit, IPU)產品Bow,其結構示意圖如圖19所示,采用臺積電SoIC-WoW(Wafer on Wafer,晶圓對晶圓)混合鍵合技術,將7 nm的處理器晶圓和供電晶圓堆疊在一起。其中,供電晶圓上含有深溝槽電容,用來存儲電荷,背面TSV允許互連至晶圓內層;較上一代相同7 nm制程,采用3D WoW封裝技術后,性能提升40%,功耗降低16%。 圖19 臺積電SoIC-WoW混合鍵合技術 中國大陸先進封裝技術發展現狀 和存在的問題 中國大陸封裝測試(簡稱封測)企業主要集中于長江三角洲地區,根據中國半導體行業協會統計,2020年中國大陸封測產品銷售額達到2509.29億元,江蘇、上海、浙江3個省份2020年封測產品銷售額合計達到1838.3億元,占2020年中國大陸封測產品銷售額的73.3%。2021年中國大陸封測產品銷售額降至2466.35億元,同比下降1.7%,2022年將再次增長,預計增至2743.44億元,同比增長11.2%,預計2026年中國大陸集成電路封測市場規模將達4551.04億元,如圖20所示。包括BGA、CSP、WLP、FO、SiP和2.5D/3D等在內的先進封裝業務占比也逐年上升,2021年中國大陸規模以上的集成電路封測企業先進封裝產品銷售額占整個封裝產業的35%左右,在保持增長勢頭的同時,與國際大廠仍有不小的差距。 圖20 2017—2026年中國大陸封測市場規模及預測 目前中國大陸產業領頭羊多注重基于解決集成電路工藝瓶頸的產業化,對于核心高端產品技術以及面向多功能與集成度的前瞻性技術缺乏相關技術布局。以長電科技、通富微電、華天科技、華進半導體為代表的封裝企業,在WLP、SiP及三維堆疊等方向實現部分產品量產與應用。開展先進封裝主要的研究機構,如中國科學院微電子研究所、中國科學院上海微系統與信息技術研究所、清華大學、北京大學、武漢大學、華中科技大學、北京理工大學、桂林電子科技大學、中國電子科技集團有限公司、中國航天科技集團有限公司等單位已形成了較強的研發力量,在晶圓級/板級扇出型封裝、異質芯片2.5D集成、Si基芯片3D疊層封裝等技術方面,經過長期的實踐摸索,形成的技術積累縮短了與國外先進封裝技術的差距。圖21為中國科學院微電子研究所聯合華進半導體開發的三維堆疊芯片封裝。 圖21 中國科學院微電子研究所聯合華進半導體開發的三維堆疊芯片封裝 與世界先進水平相比,中國大陸先進封裝技術存在以下問題。 (1)目前中國大陸封裝領域總體仍以傳統的中低端封裝為主,從先進封裝營收占總營收的比例和高密度集成等先進封裝技術發展方面,僅FC技術相對成熟,而以TSV為代表的2.5D/3D封裝和以扇出型封裝為代表的高密度扇出型技術,與國外公司的技術差距明顯,在先進封裝全球產業鏈中仍未占據重要位置,中國大陸總體先進封裝技術水平與國際領先水平還有一定的差距。未來對高端先進封裝技術的需求將越來越多,因此實現高端先進封裝技術突破越來越重要。 (2)先進封裝關鍵裝備及材料尚未實現自主可控。支撐中國大陸封裝產業鏈發展的整體基礎技術水平不高,先進封測技術所需的關鍵封裝、測試設備和材料主要依賴進口,難以滿足市場需求。 (3)先進封裝設計主要依賴境外商用EDA工具,中國大陸封裝級EDA還處于起步階段,與境外主流EDA廠商差距比較明顯,市場占有率較低,用戶反饋和迭代次數少,導致中國大陸EDA工具發展緩慢。 中國大陸先進封裝技術發展建議 針對中國大陸先進封裝領域的薄弱環節,重點攻關核心封裝工藝、關鍵封裝裝備及材料痛點,加快布局EDA工具,推進中國大陸集成電路封裝領域自主可控高質量發展。 (1)先進封裝工藝。基于明確的產業應用需求,開發合適的封裝工藝,并重點攻關核心封裝工藝,對于需在前道平臺上加工的部分工藝,需明確前道和后道工藝分工,進行前、后道協同設計和迭代優化。 (2)核心封裝材料。首先形成良好的材料—封裝—應用產業鏈,基于產業應用需求,對標國外進口材料,材料廠商開發相應的封裝材料,并測試評估和比較材料性能。然后,在國內先進封裝平臺上進行多輪迭代使用,最終實現進口材料國產化替代。 (3)關鍵封裝裝備。隨著應用需求的不斷遞進,先進封裝技術不斷升級,封裝廠商需向裝備廠商提出明確的需求,并與設備廠商協同開發關鍵封裝裝備。然后,在國內先進封裝平臺上,加快國產裝備的試用和迭代。 (4)EDA工具。發展國產EDA工具是一個漫長的過程,需要用戶不斷反饋和軟件迭代。發展國產EDA工具不僅僅局限于EDA算法和點工具研究,還需做好規劃,具有集成能力,最終形成自主可控的EDA平臺。 (5)產業鏈。預防美國針對中國大陸集成電路高端技術的進一步出口管制,加快發展中國大陸集成電路封裝領域創新聯合體,強化建設先進封裝聯合攻關公共平臺,完善國內芯粒異質集成產業鏈。 結束語 近年來,以高性能計算、人工智能和5G通信為代表的需求牽引,加速了集成電路的發展,以尺寸微縮為主線的摩爾定律發展放緩,22 nm工藝節點以下芯片的設計和制造成本呈指數級增加,芯片尺寸受限于光刻機的最大曝光面積,單一襯底上可集成的功能有限,SoC單片向芯粒異質集成“改道”是集成電路發展的重要趨勢。依據功能劃分,將原先的大尺寸SoC芯片拆成芯粒,主要功能采用先進制程,次要功能采用成熟制程,再通過先進封裝技術,實現成本較低、性能接近的集成電路產品,其中先進封裝技術不再局限于后道工藝,一些關鍵工藝需在前道平臺上進行,因此需進行前后道協同設計開發。中國需快速布局芯粒領域的技術研發,通過路徑創新,降低中國大陸集成電路發展同集成電路既有全球體系直接對沖的風險,實現靈活、高效、系統級的新型集成電路發展模式,推動集成電路的創新發展與自主可控。 END 往期推薦

?●? 綜述與述評 |劉偉平:EDA產業與IP核產業發展現狀及發展趨勢

?●? 綜述與述評 | 倪光南院士:聚焦開源RISC-V發展中國芯片產業

關于本刊 《前瞻科技》是由中國科學技術協會主管,科技導報社主辦、出版的科技智庫型自然科學綜合類學術期刊,于2022年創刊。 辦刊宗旨:圍繞國家重大戰略任務、科技前沿重要領域和關鍵核心技術,刊載相關研究成果的綜述和述評,促進學術交流,推動科技進步,服務我國經濟社會高質量發展。 常設欄目有“前瞻”“綜述與述評”“聚焦”“論壇”“文化”“書評”等,其中“前瞻”“綜述與述評”為固定欄目,其他為非固定欄目。 期刊官網:www.qianzhankeji.cn

長按識別二維碼關注我們

點擊“閱讀原文”直達期刊官網,查看全文精彩內容

(來源:Graphcore公司)

(來源:中國半導體行業協會)

●??綜述與述評 | 卜偉海:后摩爾時代集成電路產業技術的發展趨勢

●?綜述與述評 | 張衛:先進CMOS制造工藝的技術演進及自主發展思考

原文始發于微信公眾號(半導體設備與材料):綜述與述評 | 曹立強,侯峰澤:先進封裝技術的發展與機遇