?

來源:內容由半導體行業觀察(ID:icbank)編譯自semianalysis,謝謝。

在之前的報道《先進封裝最強科普》和《巨頭們的先進封裝技術解讀》中,我們對高級封裝的必要性和基本概述以及重點邏輯產品提供的主要類型、內存和圖像傳感器封裝模式進行了介紹。在本文里,我們將討論熱壓粘合 (thermocompression bonding:TCB) 以及該領域的 3 家主要工具廠商 ASM Pacific、Kulicke 和 Soffa 以及 Besi。熱壓鍵合是標準倒裝芯片工藝的演變,但涉及許多優點和缺點,我們也將在此討論。

熱壓鍵合 (TCB) 用于所有當前形式的 HBM 存儲器。英特爾的大部分封裝技術也使用 TCB。英特爾對該技術壓下了非常大的賭注,將其作為其封裝需求的驅動力,而臺積電根本沒有效仿。我們將討論這項技術如何以及英特爾在其開發中的獨特作用,這使他們能夠成為先進封裝的領導者,但我們還將討論一些缺點。英特爾希望繼續在 TCB 工具上花費數億美元的訂單,用于在亞利桑那州、新墨西哥州的擴張以及在馬來西亞新建的 70億美元封裝設施中。我們將首先解釋該技術、英特爾在該技術開發中的主要作用,最后是工具生態系統。

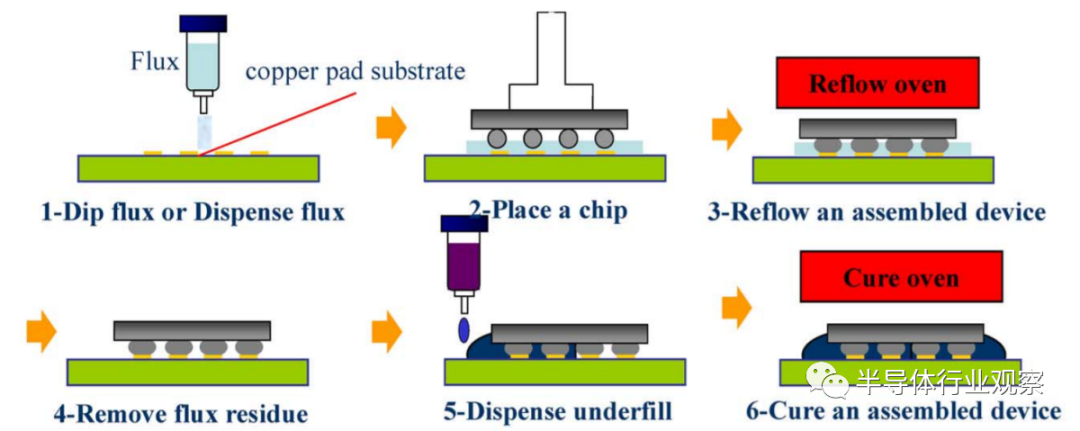

要了解TCB的優勢,首先要說一下倒裝芯片封裝的弊端。如在《巨頭們的先進封裝技術解讀》中所述,標準倒裝芯片工藝從沉積助焊劑或非導電漿料開始。然后,芯片放置工具將芯片準確地放置在基板、中介層或載體上。這是在批處理過程中完成的,因此許多封裝可以一次放置它們的裸片。然后將放置的模具組進入回流爐,這也是一個批處理過程。將數十個、數百個甚至數千個封裝放入烤箱中,加熱到使焊料熔化的溫度以完成粘合,然后繼續進行后續步驟,例如去除助焊劑殘留物和底部填充。

這個過程非常快,但也有一些主要缺點。最大的問題與熱膨脹系數 (coefficient of thermal expansion:CTE) 有關。因為整個封裝由許多不同的材料組成,在回流爐中加熱會導致這些不同的材料以不同的速率膨脹。下面我們將舉個例子,雖然這不是最好的類比,但還是有參考意義。如果你曾經烤過餡餅,你就會知道餡餅皮,餡餅的餡料不會以同樣的速度膨脹。如果您對幾個不同的因素不小心,您的餡料最終會在外殼的頂層沸騰并使外殼濕透。

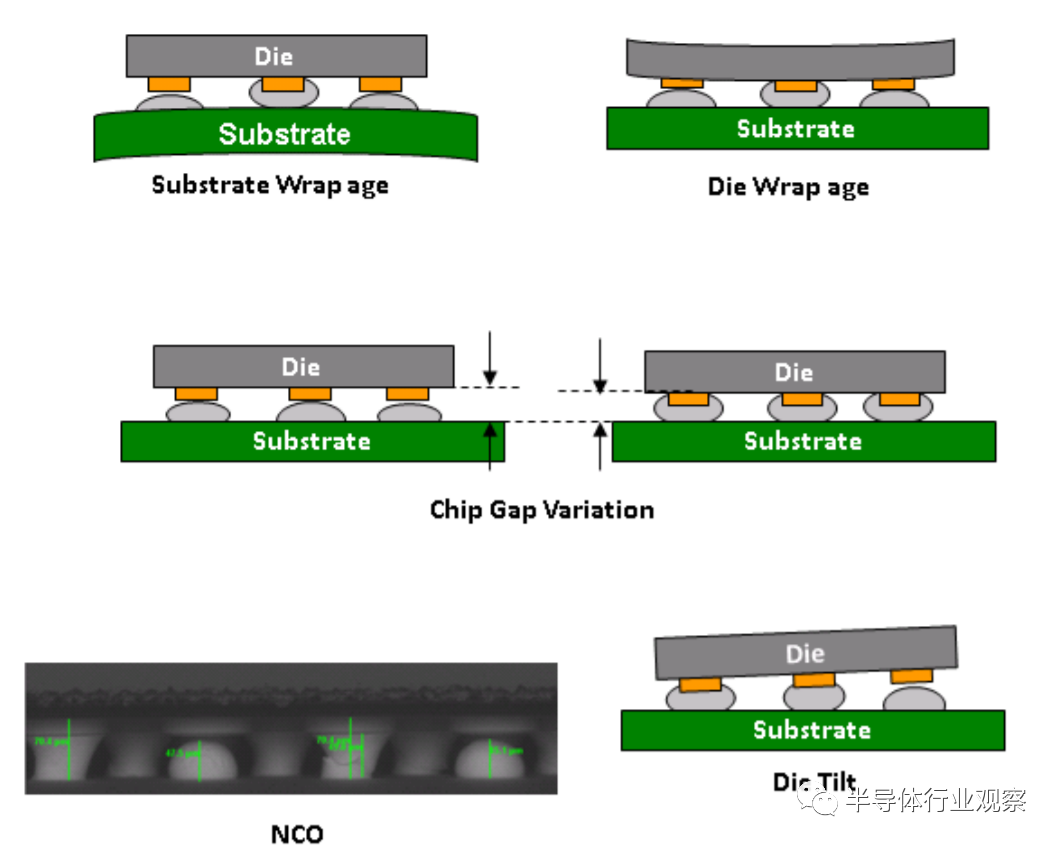

隨著芯片和基板膨脹和冷卻,CTE 的差異會導致翹曲。此外,由于芯片是放置后重新焊接的,焊球可能無法與每個銅焊盤完美接觸,從而導致芯片間隙變化。最后,Die可能無法完全平整放置。隨著時間的推移,這些小問題會累積起來,導致早期故障或更差的電氣性能。

業界只能關注許多原始的無源中介層技術。AMD 基于Fiji的 GPU 的故障率非常高,因為該過程沒有產生完美的粘合,最終熱循環導致產品無法正常工作。隨著 TSMC 和 ASE/SPIL 學會了如何進行基于中介層的封裝,這些可靠性問題隨著時間的推移而有所改善,但尚未完全解決。在溫度不穩定且封裝頻繁在高溫和低溫之間循環的環境中,這些問題仍然比較常見。

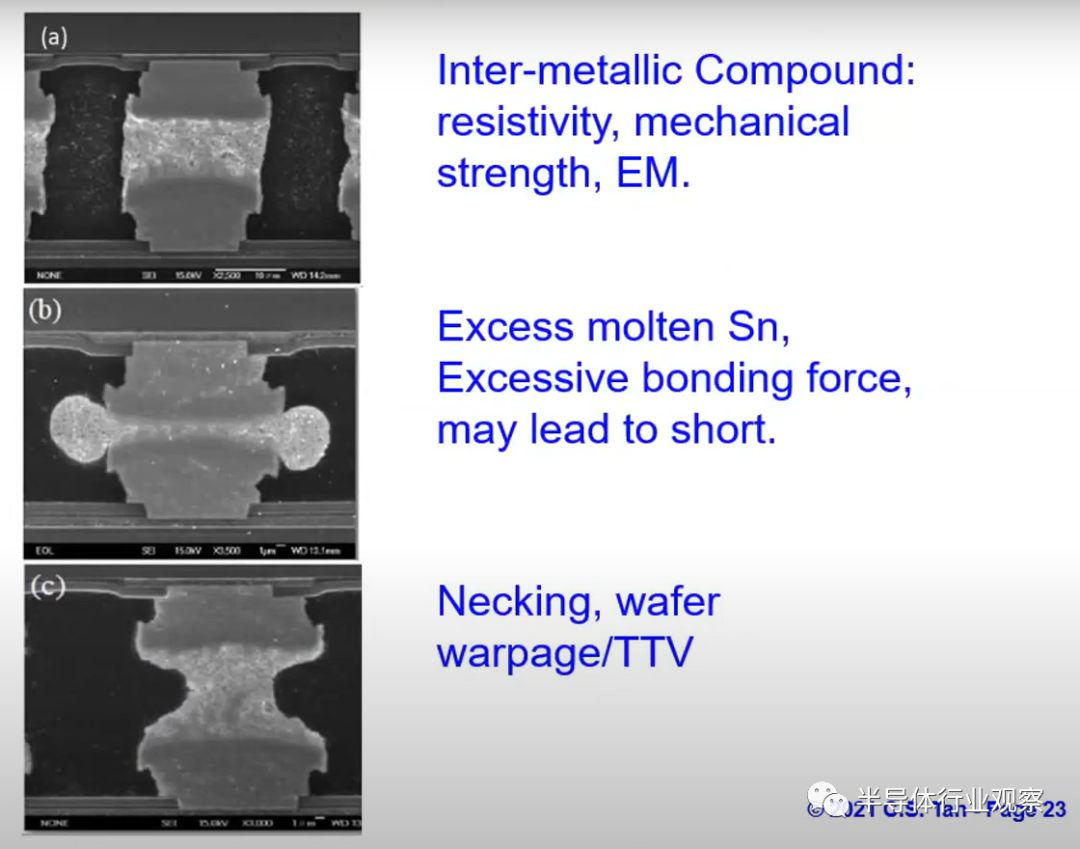

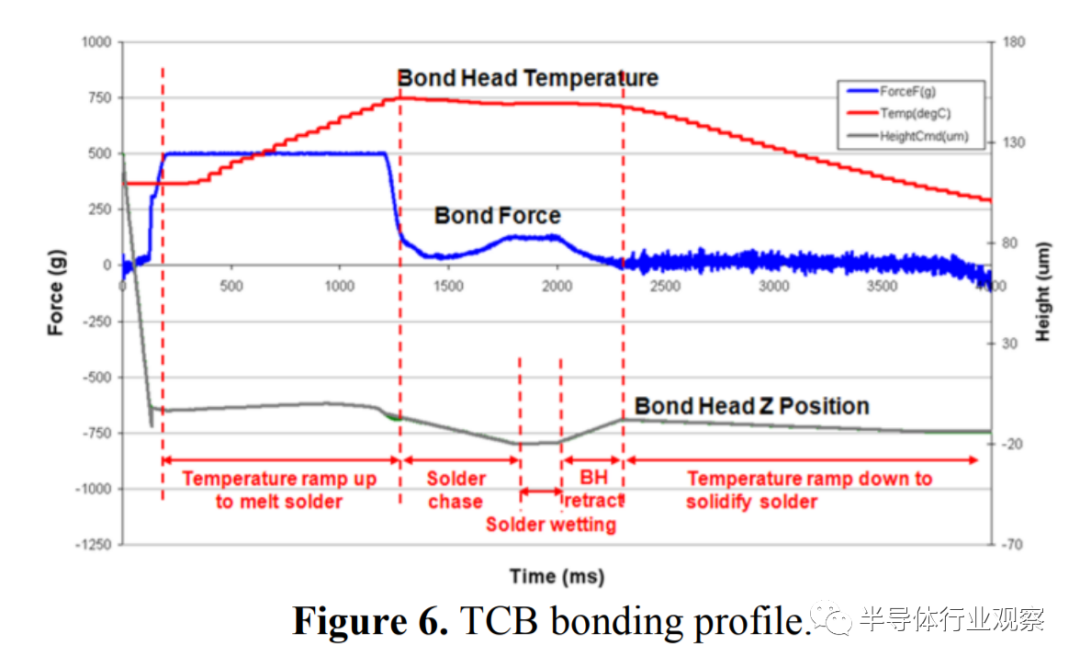

來到熱壓粘合。雖然我們無需在批處理過程中放置芯片并將整個組件運送到回流爐,而是使用單一工具放置單個芯片,施加壓力并加熱它們以回流焊球。這種方式解決了標準倒裝芯片的幾個主要問題。從芯片頂部加熱,因此只有芯片和 C4 焊接連接會發熱。這避免了基板翹曲問題。該力確保均勻粘合,沒有間隙變化或傾斜。最后,當施加該力時,會伴隨著快速振動,從而破壞銅焊盤和焊球上的金屬氧化。幾乎沒有空隙和污染的粘合。

TCB 在相同的 IO 間距下實現更好的電氣特性。TCB 允許 IO 間距縮放到更小的尺寸。TCB 還可以封裝更薄的芯片和封裝。后者是 HBM 使用 TCB 的原因,也是華為在移動芯片市場上嘗試使用 TCB 的原因。與標準倒裝芯片工藝流程相比,TCB 似乎是一種完全更好的技術,但這忽略了一個主要因素。

再看成本,一個先進的 TCB 工具每小時可放置 500 到 1,000 個Die,成本約為 125 萬美元。另一方面,先進的倒裝芯片芯片放置工具每小時可放置 3,000 到 10,000 個芯片,成本約為 450k。這些數字差異很大,具體取決于精度與吞吐量的權衡以及工具可能附帶的各種功能,但其明顯的標準倒裝芯片的吞吐量要高得多。回流爐非常便宜,可以處理許多貼片工具的輸出,因此成本不值得擔心。

令人好奇的是,英特爾擁有近 300 種 TCB 工具,而在馬來西亞的封裝工廠,這些工具的數量翻倍。這 300 種工具遠遠超過了英特爾的先進封裝用途。英特爾在許多非高級封裝應用中使用 TCB,在這些應用中,標準的倒裝芯片工藝非常適合。

SemiAnalysis 私下與一位英特爾封裝工程師進行了交談,理由很有趣。鑒于英特爾在高功率和高利潤應用中占有很大份額,產量損失和可靠性問題遠遠超過了每單位封裝工具的微不足道的攤銷成本。

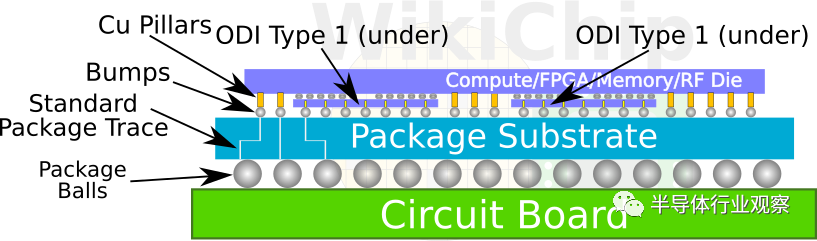

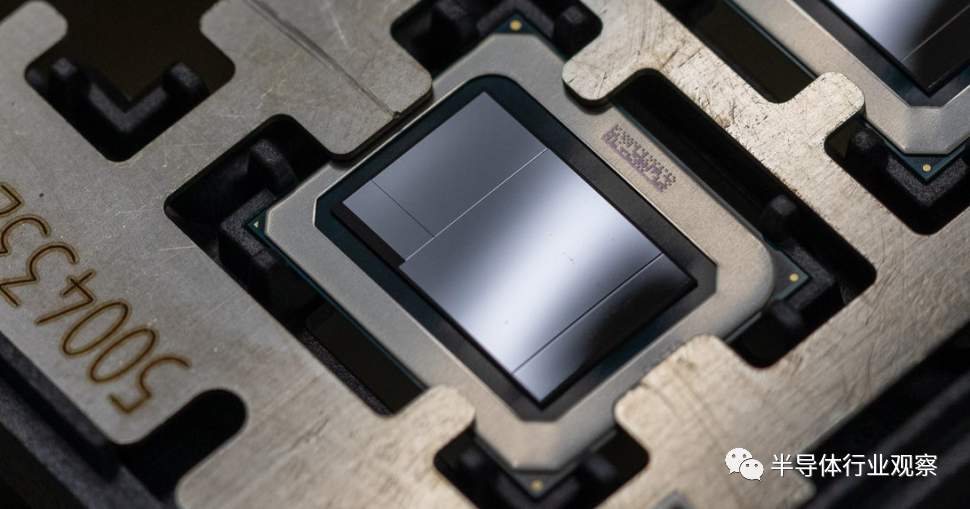

此外,這些工具在封裝類型方面提供了很大的靈活性。英特爾可以對標準封裝、2.5d 封裝和高級 3d 封裝使用相同的工具。上圖來自der8auer,它展示了具有多種間距尺寸的 Intel Sapphire Rapids 服務器 CPU。EMIB 的間距為 55 微米,其余的Die與封裝連接的間距為 100 微米。雖然理論上這在沒有 TCB 的情況下是可能的,但考慮到焊盤和焊帽尺寸的差異,在現實世界中的實施要容易得多。

當英特爾轉向 Foveros Omni 時,TCB 的功能真正開始大放異彩。我們在上述文章中討論了該技術,但銅柱和 ODI 裸片使 Foveros Omni 幾乎無法使用標準倒裝芯片工藝進行封裝。第一款 Foveros Omni 產品將是英特爾的 Meteor Lake,這是一種大眾市場客戶端架構,專為 5W SOC 一直到高功率臺式機而設計。盡管包含許多裸片,Omni 仍可大幅節省制造成本,為 IP 選擇最佳工藝節點并最小化裸片尺寸以提高產量。該封裝具有 130 微米、100 微米和 36 微米的各種凸塊間距。高級 3D 邏輯封裝不僅適用于高性能應用。

臺積電、三星和許多其他公司將無法進行這種封裝,除非他們在 TCB 上投入巨資。十多年來,英特爾一直在共同開發 TCB 工具,因此競爭對手很難立即轉向這項技術。臺積電的 InFO 采用標準倒裝芯片流程,同時由于基板更昂貴,可能是一種更昂貴的封裝技術。臺積電沒有先進的封裝,而是在商品標準的 ABF 基板上,這阻礙了他們在成本方面能夠將先進封裝降低多遠。同時,InFO 確實具有我們在第 2 部分中討論的一些主要優勢,即與 RDL 內的復雜布線相關,無需使用硅片。

混合鍵合的功能超出了倒裝芯片 TCB 所能提供的任何功能,但該技術在成本和性能曲線上的運行點完全不同,這削弱了其在中期內增加產量的能力。這將在未來討論。

英特爾對 TCB 的支持使他們能夠圍繞各種 IP 創建可選性,并在許多不同的節點上制造許多不同的塊,而不會對 die-to-die 連接造成很大的損失。設計方面的策略細節在這篇關于英特爾臺積電晶圓供應協議的文章中進行了討論。

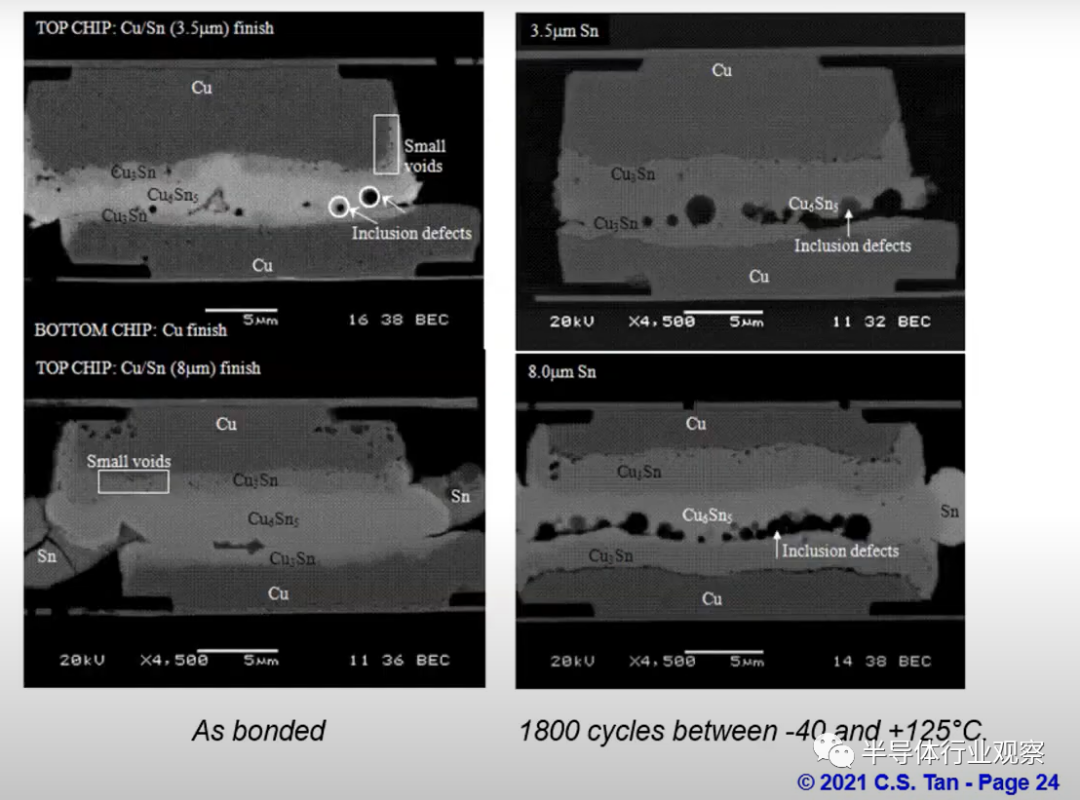

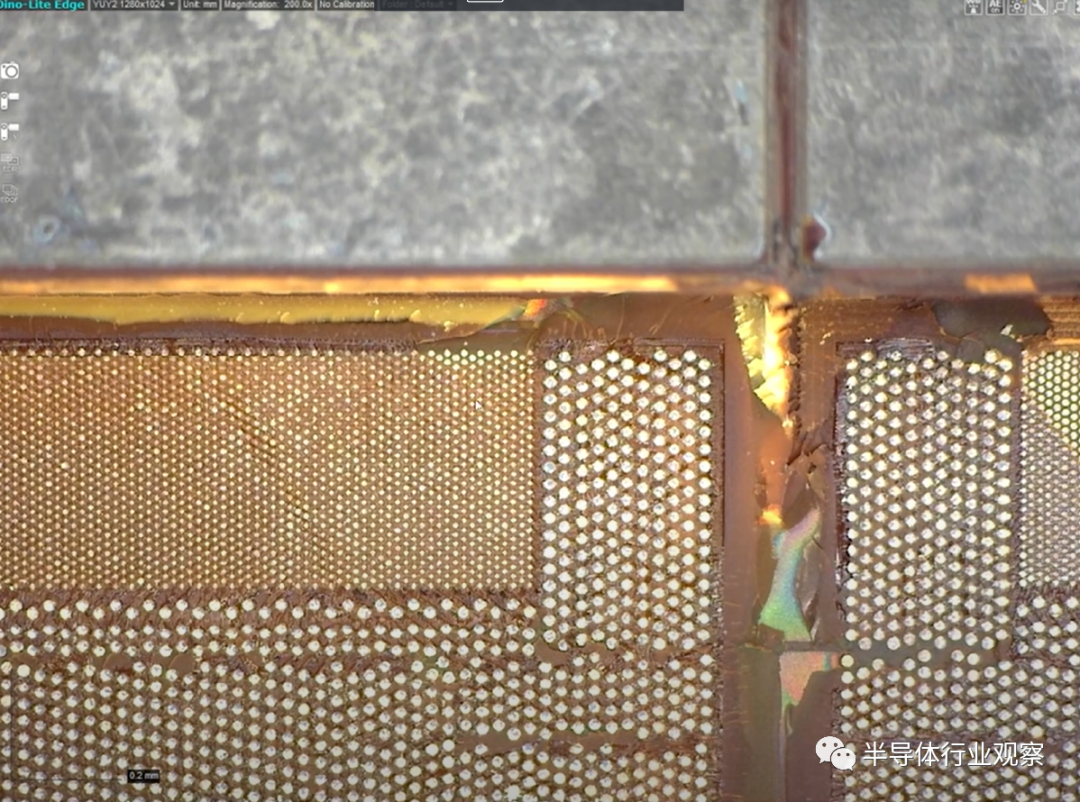

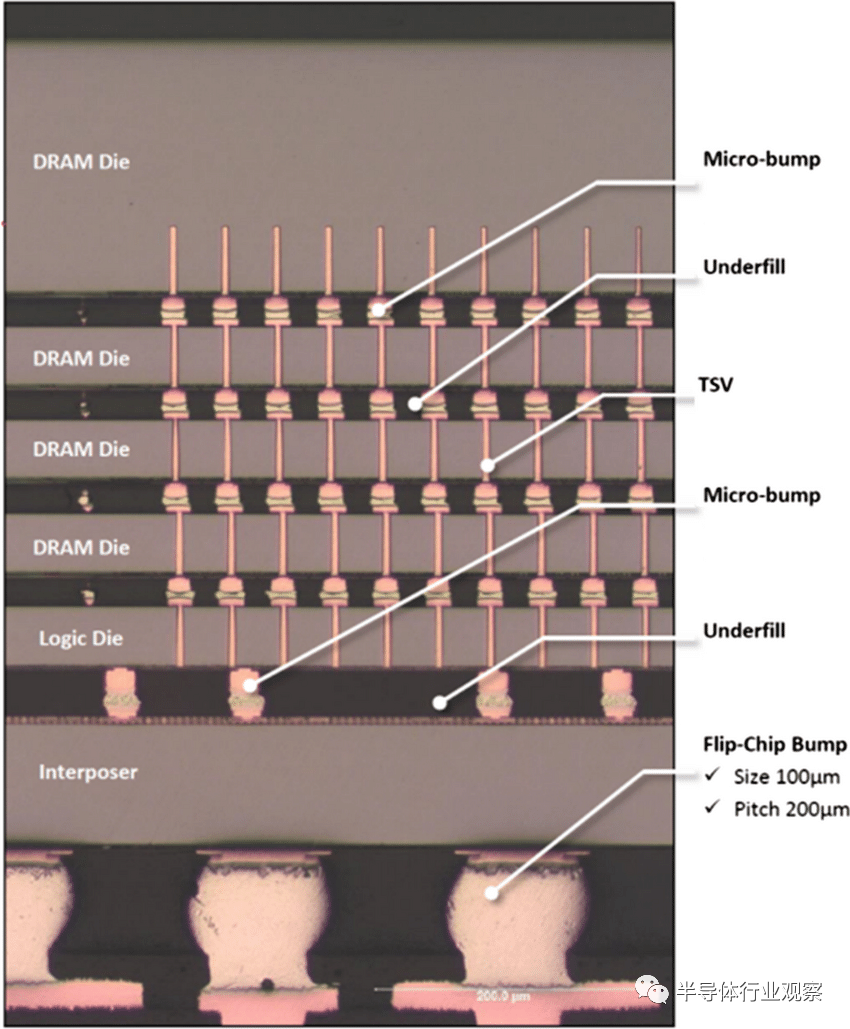

TCB 也已在 HBM 應用中采用。HBM die需要非常薄。上圖只有 4 個堆棧,但隨著行業擴展到 8 個堆棧甚至更多,三星、SKHynix 和美光必須使用 TCB。在 SKHynix 即將推出的 12 堆棧 HBM3 中,對裸片薄度的要求變得如此極端,每個裸片都被減薄到 30 微米。凹凸間距同樣非常密集。目前啟用 HBM 堆棧的唯一方法是使用 TCB 技術,但業界期待可能使用更奇特的封裝形式,例如混合鍵合。

由于 TCB 是封裝極薄芯片的最佳技術,因此 TCB 還通過使用 OSAT 和 IDM 封裝的旗艦設備中的手機應用進行了試驗。三星、高通/Amkor 和華為/ASE 在一些與封裝上封裝 (PoP) DRAM 相關的應用中使用了 TCB。OSAT 開始訂購越來越多的 TCB 工具,但最大的訂單仍然來自英特爾及其定制的共同開發的 TCB 平臺。關于這些其他用例需要注意的重要一點是,它們與英特爾的工具不同,它們也不是為高功率或高性能應用而設計的。

ASM Pacific、Kulicke 和 Soffa 以及 Besi 之間的市場對 TCB 來說是非常活躍的,并且每家都在不同的領域表現出色。這導致每個人都有自己的利基市場。訂單簿正在大幅上升,但由于它們各自占據的利基市場,這三個方面并不一致。

原文始發于微信公眾號(半導體行業觀察):先進封裝,英特爾在這個環節領先臺積電